Trigger unit single event upset effect experimental verification circuit

A single event flipping and verifying circuit technology, which is applied in the field of trigger unit single event flipping effect experimental verification circuit, can solve the problem of large power consumption without considering the flip-flop data, without considering the jump of the input signal, and increasing the complexity of the evaluation method and other problems, to achieve the effect of avoiding large transient power consumption, reducing instantaneous voltage drop, and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

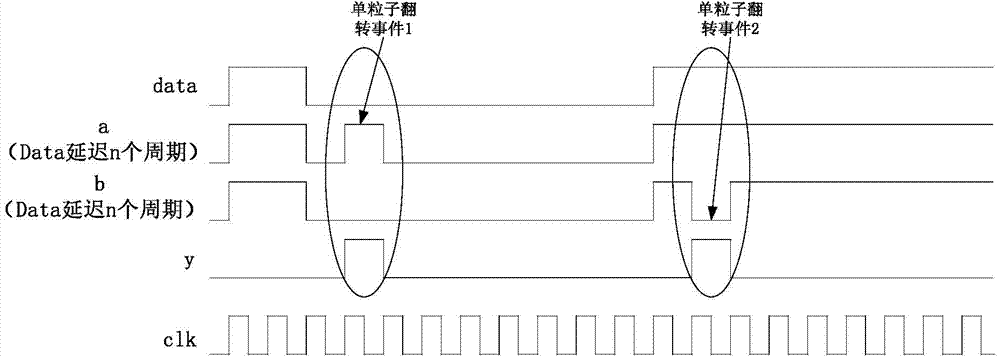

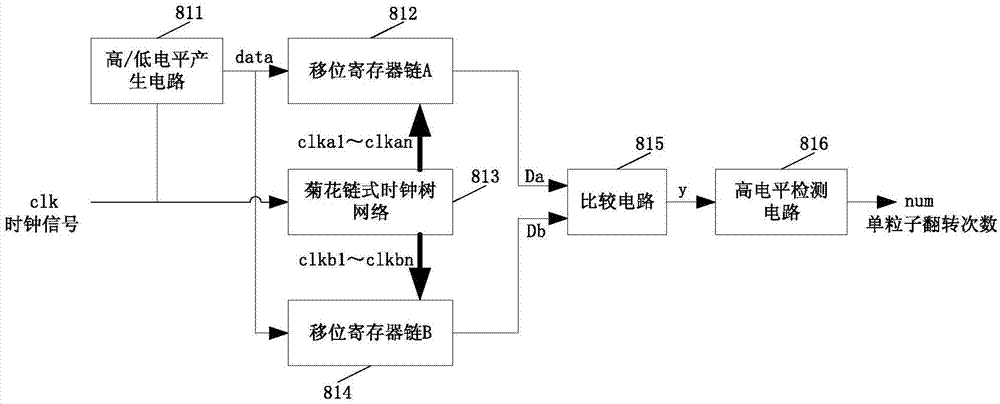

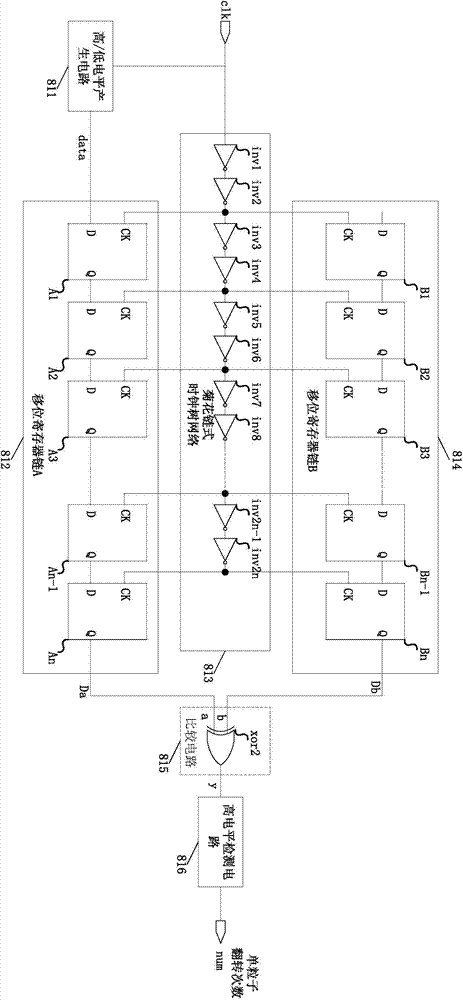

[0023] The present invention is a flip-flop unit single event flip effect experimental verification circuit, such as figure 2 As shown, it includes a high / low level generation circuit 811, a shift register chain A812 and a shift register chain B814, and a daisy-chained clock tree network 813 and a high level detection circuit 816; a high / low level generation circuit 811 The input terminal of the high / low level generating circuit 811 is connected with the clock signal clk, and the output terminal of the high / low level generating circuit 811 outputs the periodic high and low level signal data, and is connected with the input terminals of the shift register chain A and the shift register chain B; The input end of the bit register chain A812 is also connected to the output ends clka1˜clkan of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More