Wafer-level test structure and test method for a DRAM chip

A test structure, wafer-level technology, applied in static memory, instruments, etc., can solve the problem of occupying chip area and increase cost, and achieve the effect of reducing chip area, improving utilization rate, and reducing chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

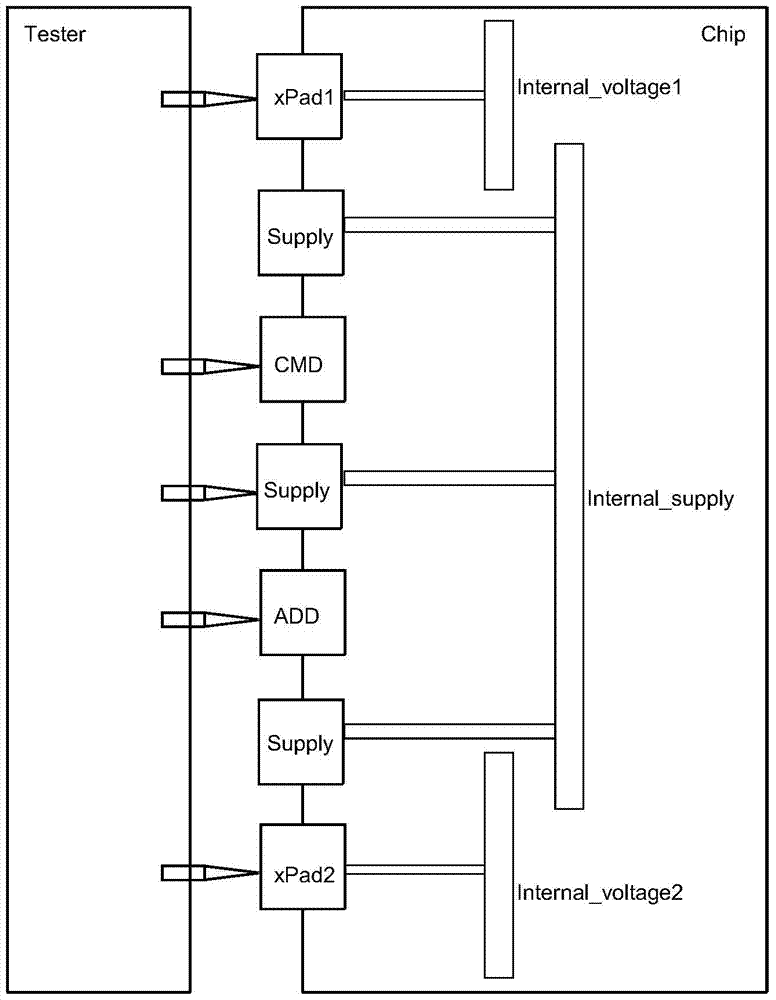

[0024] A wafer-level test structure of a DRAM chip of the present invention, such as Figure 4 As shown, it includes a first power supply pad and a second power supply pad respectively connected to the internal power supply network of the DRAM chip; the second power supply pad is connected to the internal power supply network through a power supply path, and the second power supply pad is connected to the internal voltage The network is set through the connection of the voltage path, and the voltage path is set in parallel on the power path; the voltage path and the power path are respectively connected to the first transmission gate and the second transmission gate through the input and output terminals, and the control of the first transmission gate and the second transmission gate The pola...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More