Manufacturing method for interconnected through holes in wafer level chip size packaging

A wafer-level chip and size packaging technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that affect the reliability of packaged chips, circuit short circuits, complex process steps, etc., and achieve simple methods and improve reliability. performance, the effect of simple encapsulation steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Such as figure 1 , figure 2 , image 3 , Figure 4 , Figure 5 , Figure 6 , Figure 7 , Figure 8 and Figure 9 As shown, a method for manufacturing through-hole interconnection in a wafer-level chip size package, comprising the following steps:

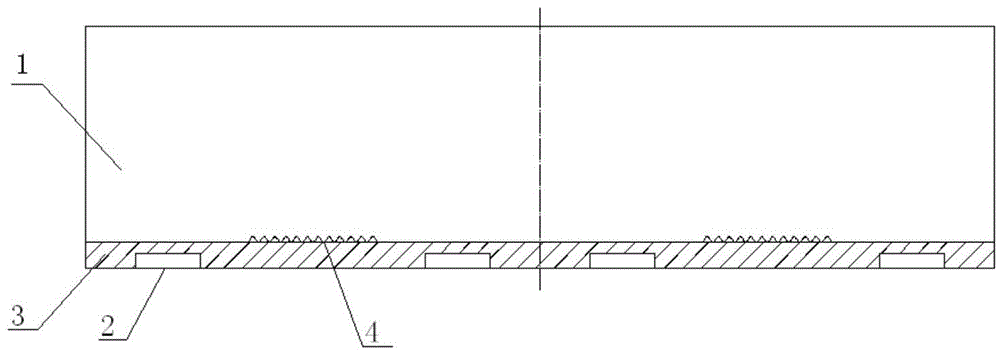

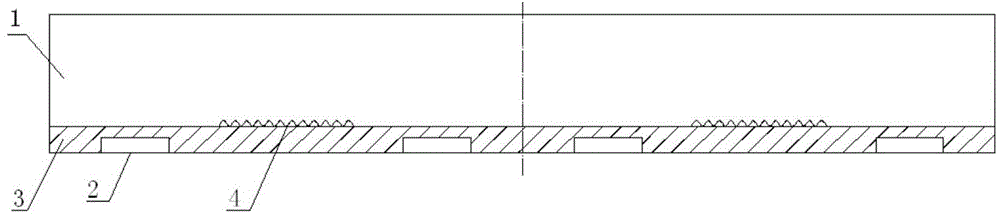

[0045] a. see figure 1 , provide a wafer with several chip units, the chip unit includes a base 1 and a dielectric layer 3 on the front side of the base 1, the front side of the base 1 is provided with an element area 4, and the periphery of the element area 4 A plurality of welding pads 2 are provided, and the welding pads 2 are located in the dielectric layer 3, and the element area 4 is electrically connected to the surrounding welding pads 2;

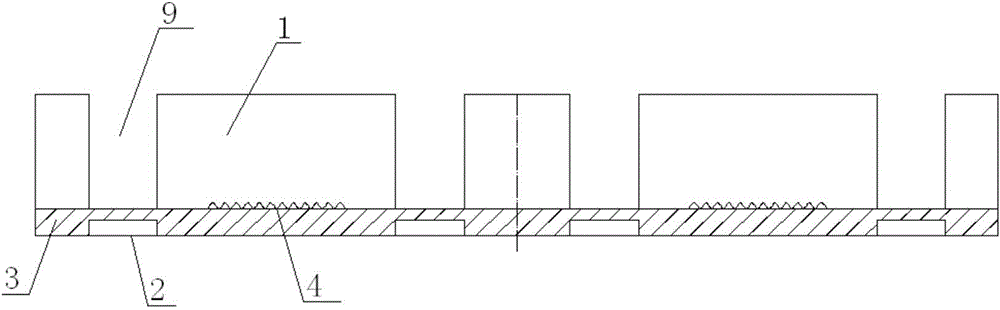

[0046] b. see image 3 A first opening 9 opposite to the welding pad 2 is formed on the back of the substrate 1, and the first opening 9 extends from the back of the substrate 1 to above the corresponding welding pad 2, and exposes the welding pad 2, that is, there is a...

Embodiment 2

[0062] Such as Figure 10 and Figure 11 As shown, this embodiment 2 includes all the technical features in the above embodiment 1, the difference is that step b is replaced by: forming a first opening 9 opposite to the welding pad 2 on the back of the substrate 1, and the The first opening 9 extends from the back of the substrate 1 to above the corresponding pad 2 and exposes the surface of the pad 2 . Step d is replaced by: removing the photoresist layer 5 above the welding pad 2 through a photolithography process to expose the surface of the welding pad 2 . That is, according to the extent to which the first opening 9 extends toward the back of the substrate 1 , the barrier material on the pad 2 may include the material of the photoresist layer 5 or a combination of the material of the dielectric layer 3 and the material of the photoresist layer 5 . For example, when the surface of the welding pad 2 is exposed, the barrier material on the welding pad 2 is only the photore...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More