A method for improving the breakdown voltage of gate oxide layer of trench vdmos device

A gate oxide layer and oxide layer technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as lower breakdown voltage, device IGSS failure, and epitaxial layer surface damage, so as to improve the breakdown voltage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] A method for improving the breakdown voltage of the gate oxide layer of the trench type VDMOS device of the present invention may comprise the steps of:

[0030] Step 1, providing a silicon substrate with an epitaxial layer;

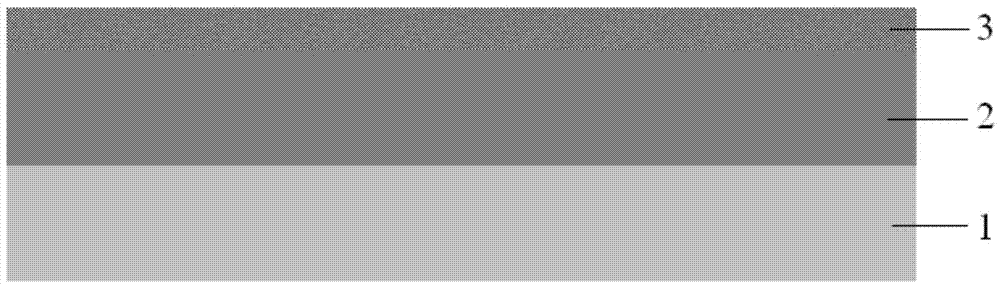

[0031] Specific as figure 1 As shown, the silicon substrate with an epitaxial layer can be a conventional epitaxial wafer in this field, and an epitaxial layer 2 can also be grown on a silicon substrate 1 by a conventional method in this field; An N-type epitaxial layer 2 is formed on one side surface of the silicon substrate 1 .

[0032] Step 2, forming an initial oxide layer on the epitaxial layer of the silicon substrate;

[0033] Specifically, the epitaxial layer 2 of the silicon substrate 1 can be formed by wet oxidation with a thickness of The initial oxide layer 3; in this embodiment, the thickness of the formed initial oxide layer 3 can be The temperature of wet oxidation may be 950°C.

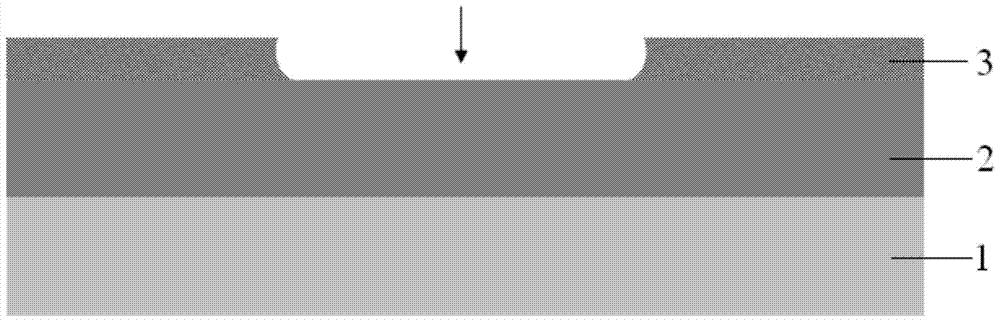

[0034] Step 3, photolithography and etching, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More