Method for forming shallow trench

A shallow trench and amorphous carbon technology, which is applied in the manufacture of electrical components, semiconductor/solid-state devices, and circuits, can solve the problems of large differences in the depth of shallow trenches and lower yields, so as to alleviate the difference in etching amount and ensure The effect of yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

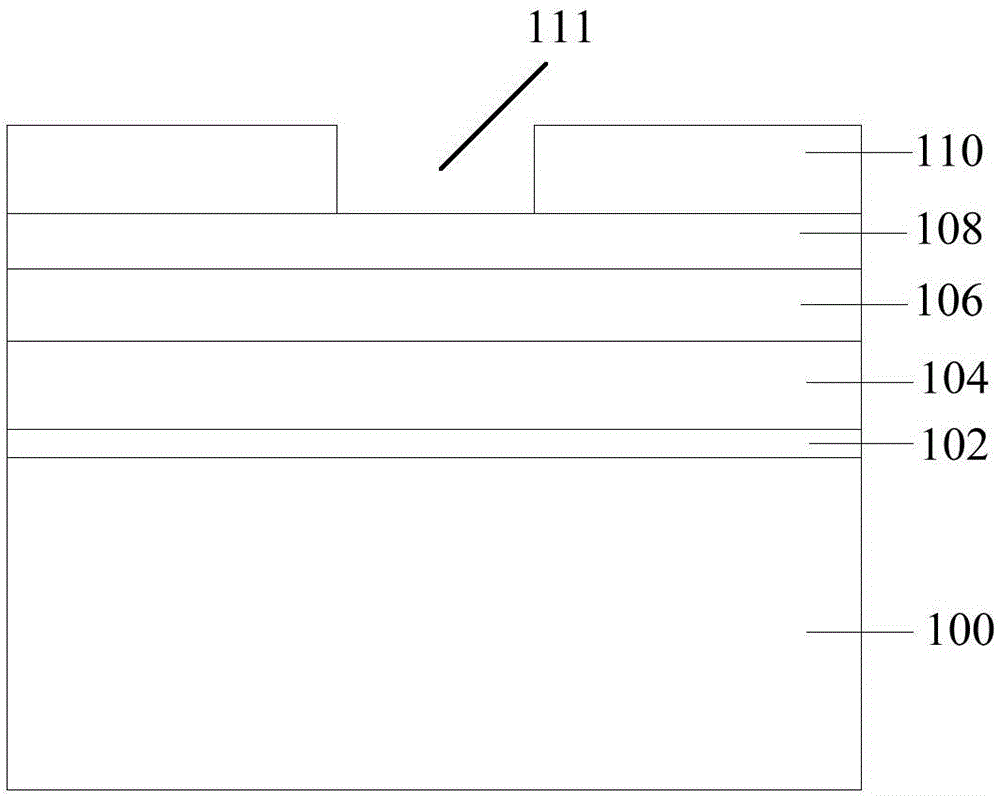

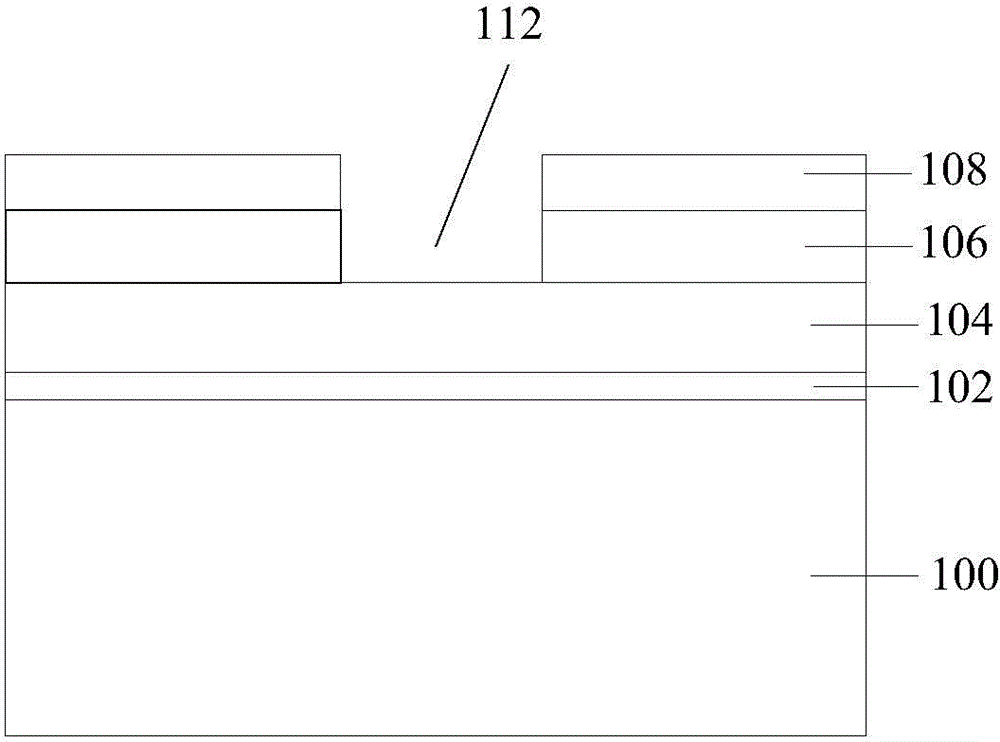

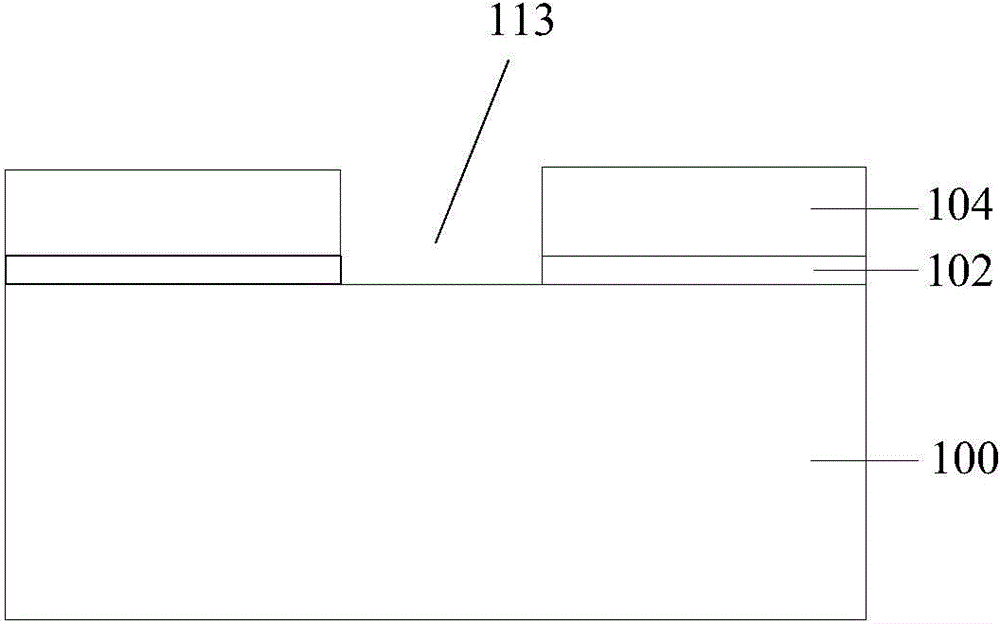

[0033] In the existing process of forming shallow trench isolation to separate the active area, due to the slight asymmetry of the plasma distribution in the reaction chamber or the slight difference in the etching rate, the film layer at different positions of the wafer after the same process step The amount of etching will be different, and if the formation of shallow trenches requires a multi-step etching process, then after the accumulation of differences, the depth of the final formed shallow trenches will vary greatly at different positions, resulting in a decrease in yield.

[0034] In order to solve this problem, the present invention adjusts the horizontal angle of the wafer before each step of etching in the process of forming the shallow trench, so that the final adjusted angle is consistent with the maximum asymmetry, so as to alleviate the unevenness of the etching amount. The depth of the finally formed shallow trenches at different positions is consistent, which ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com