Method for verifying large-scale interconnection chips based on BFM

A chip and large-scale technology, applied in the field of chip design, can solve the problems of unable to meet the verification requirements of interconnected chips, increase the workload and complexity of integrated circuit verification, achieve high operation and data monitoring, reduce complexity, and improve verification efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

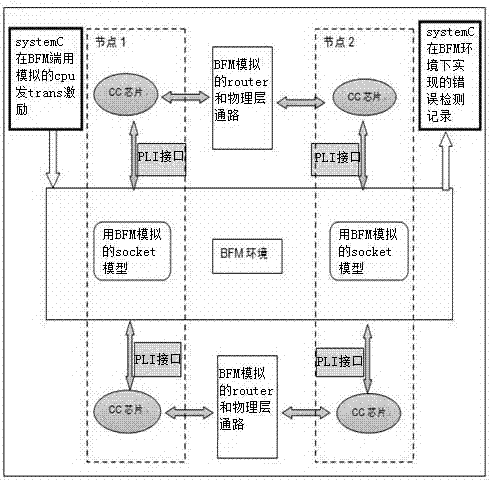

[0015] Intel's BFM environment is written in system C code, which can be connected to verilog's testbench through the pli interface, and we can use system C code to write various incentives, monitoring mechanisms and corresponding rules under BFM. The verification method based on BFM can quickly complete the verification of large-scale interconnected chips at a higher level, better meet the chip verification requirements, and provide important support and quality for subsequent FPGA (Field Programmable Gate Array) verification and mass production chips ensure.

[0016] A method for verifying large interconnected chips based on BFM,

[0017] In the testbench environment, use BFM to simulate the router and physical layer path of chips between nodes to realize the operation of sending bus protocol commands; BFM is connected to the chip of the same node through the pli interface, BFM simulates the socket model between nodes, and the The code is encapsulated in the form of subrout...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More