Thin film transistor and production method of thin film transistor, array substrate and display equipment

A technology of thin film transistor and manufacturing method, which is applied in transistor, semiconductor/solid-state device manufacturing, semiconductor device and other directions, can solve the problems of poor display quality, uneven gate line resistance, and gate line bulging.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

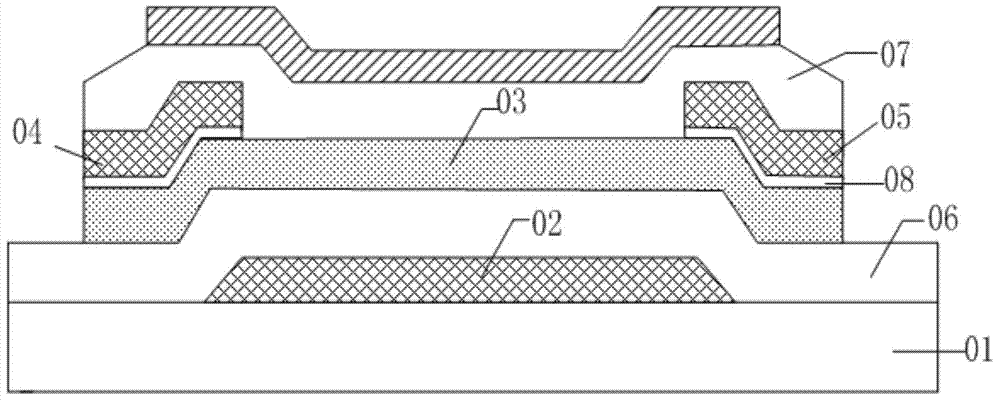

Image

Examples

Embodiment 1

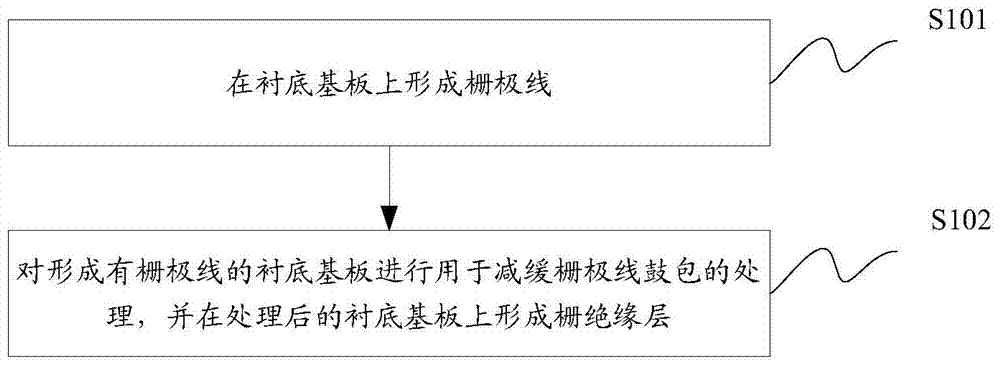

[0049] see image 3 , a method for fabricating a thin film transistor provided in an embodiment of the present invention includes:

[0050] S201, forming a gate line on the base substrate;

[0051] S202, directly forming a gate insulating layer on the base substrate on which the gate lines are formed;

[0052] In this embodiment, the gate insulating layer is directly formed on the base substrate on which the gate line is formed, that is, the N2 plasma treatment step is omitted. Since the plasma treatment is to obtain plasma by heating for bombardment treatment, omitting this step will greatly reduce the The temperature at which the gate lines are heated reduces the temperature at which the gate lines are heated and prevents the grid lines from bulging.

[0053] S203 , respectively forming an active layer, a source electrode, a drain electrode, a passivation layer, a common electrode, and a pixel electrode on the base substrate on which the gate insulating layer is formed.

Embodiment 2

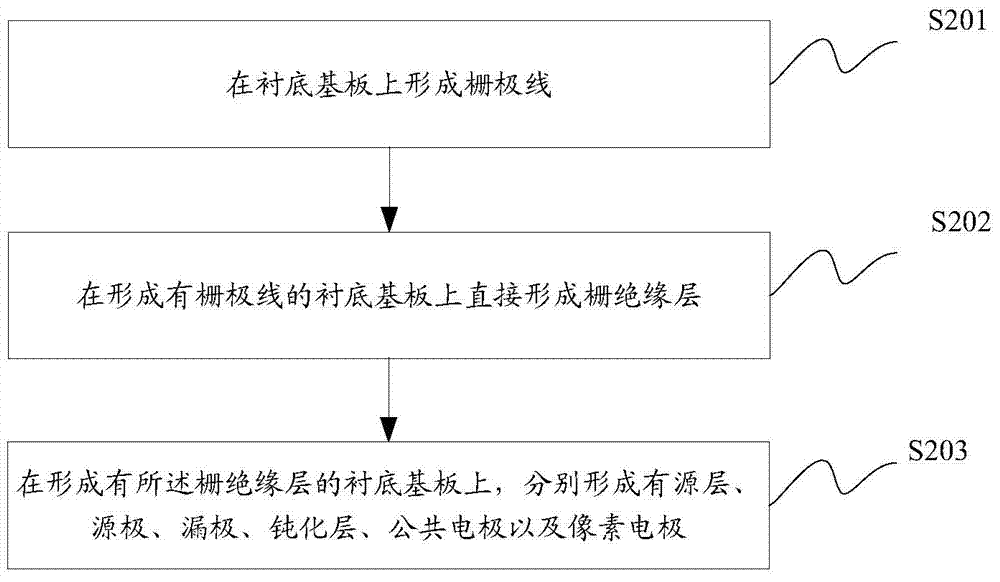

[0055] see Figure 4 , a method for fabricating a thin film transistor provided in an embodiment of the present invention includes:

[0056] S301, forming a gate line on the base substrate;

[0057] S302. Perform plasma treatment on the gate lines with a preset plasma treatment power, and form a gate insulating layer on the base substrate on which the gate lines are formed after the plasma treatment, wherein the preset plasma treatment The power is less than 8 kW.

[0058] In this embodiment, the power of the plasma treatment is reduced. Since the plasma treatment is bombarded by heated plasma, reducing the power of the plasma treatment also reduces the temperature of the plasma treatment, thereby reducing the heating temperature of the grid line and avoiding the grid line. Extreme line drum kit.

[0059] S303 , respectively forming an active layer, a source electrode, a drain electrode, a passivation layer, a common electrode, and a pixel electrode on the base substrate on...

Embodiment 3

[0061] see Figure 5 , a method for fabricating a thin film transistor provided in an embodiment of the present invention includes:

[0062] S401, forming a gate line on the base substrate;

[0063] S402. According to the preset preheating time, perform preheating treatment on the base substrate formed with the gate lines, and form a gate insulating layer on the preheated base substrate formed with the gate lines, wherein the The preset warm-up time mentioned above is less than 60 seconds;

[0064] In this embodiment, by reducing the preheating time, the heating time of the gate lines is shortened, thereby reducing the temperature at which the gate lines are heated, and avoiding the swelling of the gate lines.

[0065] Through specific experiments, it can be known that when the preheating time is within the range of 10 seconds and 20 seconds, the swelling problem of the gate lines will be alleviated to the greatest extent, and the oxidation degree of the gate lines will be s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More