A method for improving the breakdown voltage of gate oxide layer of trench vdmos device

A gate oxide layer and oxide layer technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of lower breakdown voltage, surface damage of epitaxial layer, and degradation of gate oxide layer quality, so as to improve the breakdown voltage. Breakthrough voltage, improvement of failure ratio, and quality assurance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

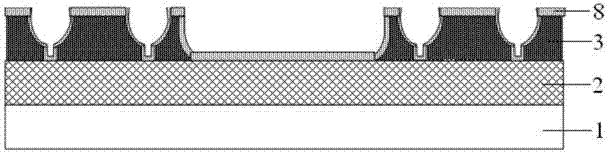

[0032] A method for improving the breakdown voltage of the gate oxide layer of the trench type VDMOS device of the present invention may comprise the steps of:

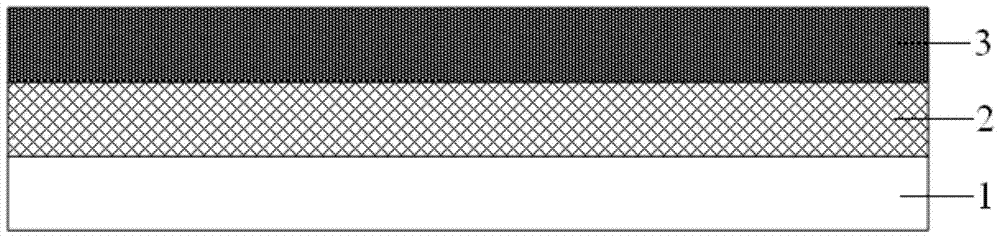

[0033] Step 1, providing a silicon substrate with an epitaxial layer;

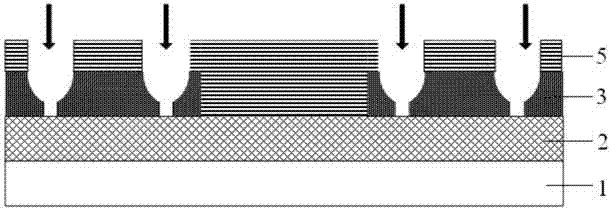

[0034] Specific as figure 1 As shown, the silicon substrate with an epitaxial layer can be a conventional epitaxial wafer in this field, and an epitaxial layer 2 can also be grown on a silicon substrate 1 by a conventional method in this field; An N-type epitaxial layer 2 is formed on one side surface of the silicon substrate 1 .

[0035] Step 2, forming an initial oxide layer on the epitaxial layer of the silicon substrate;

[0036] Specifically, the epitaxial layer 2 of the silicon substrate 1 can be formed by wet oxidation with a thickness of The initial oxide layer 3; in this embodiment, the thickness of the formed initial oxide layer 3 can be The temperature of wet oxidation may be 950°C.

[0037] Step 3, photolithography and etching, ...

Embodiment 2

[0055] Except step 10, the thickness of the gate oxide layer is Except, other is identical with embodiment 1. After testing, the breakdown voltage of the gate oxide layer of the trench VDMOS device in this embodiment is 94V.

Embodiment 3

[0057] Except step 10, the thickness of the gate oxide layer is Except, other is identical with embodiment 1. After testing, the breakdown voltage of the gate oxide layer of the trench VDMOS device in this embodiment is 50V.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More