Semi-super-junction MOSFET structure and manufacturing method thereof

A fabrication method and semi-superjunction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as process capability limitations, and achieve the goal of expanding application fields, high withstand voltage capability, and increasing withstand voltage range. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

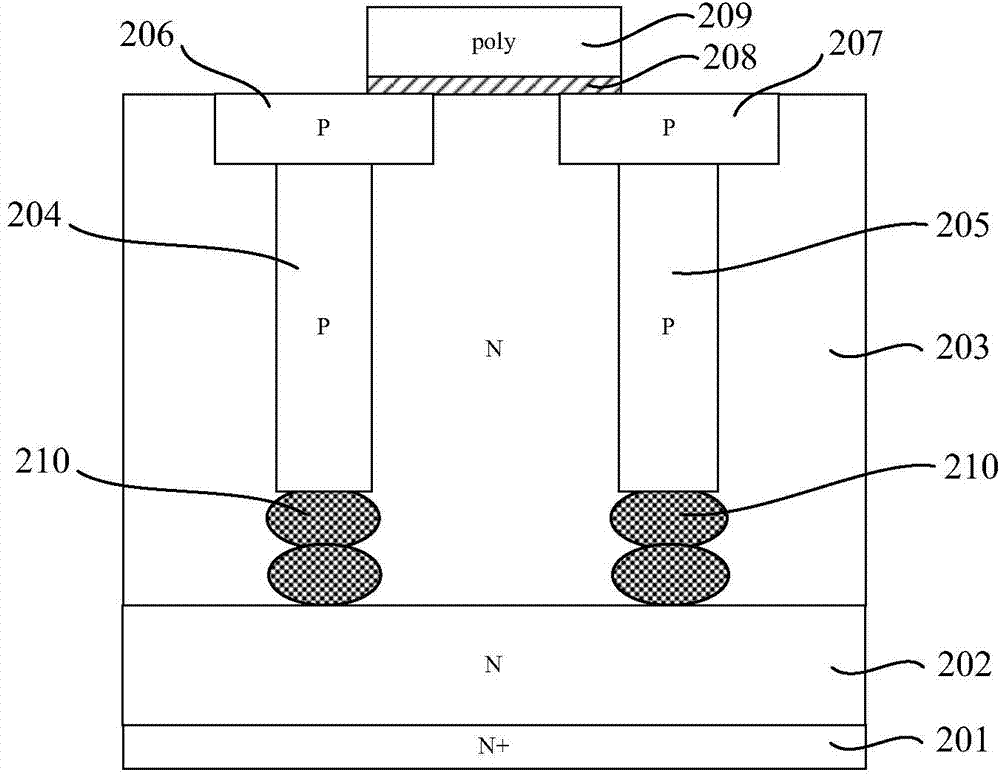

[0076] The present invention provides a semi-superjunction MOSFET structure, please refer to image 3 , shown as a schematic diagram of the structure, comprising at least one transistor cell comprising:

[0077] An N-type heavily doped substrate 201 and an N-type auxiliary layer 202 and an N-type drift layer 203 sequentially formed on the N-type heavily doped substrate 201;

[0078] A first P column 204 and a second P column 205 are formed in the N-type drift layer 203;

[0079] The first P-type body region 206 and the second P-type body region 207 are connected to the tops of the first P-pillar 204 and the second P-pillar 205 respectively, and the first P-type body region 206 and the second P-type body region 207 is located in the N-type drift layer 203;

[0080] A gate structure is formed on the surface of the N-type drift layer 203; the gate structure is located between the first P column 204 and the second P column 205, and both ends of the gate structure are connected t...

Embodiment 2

[0089] The present invention also provides a method for fabricating a semi-superjunction MOSFET structure, comprising the following steps:

[0090] See first Figure 5 , performing step S1: providing a semiconductor substrate sequentially comprising an N-type heavily doped substrate 201 and a first N-type epitaxial layer 215 from bottom to top, and performing P-type impurity implantation on the top of the first N-type epitaxial layer 215 , forming a first pair of P island structures 2101 arranged at intervals. Wherein, the part of the first N-type epitaxial layer 215 below the first pair of P-island structures serves as an N-type auxiliary layer of the semi-superjunction MOSFET.

[0091] then see Figure 6, performing step S2: forming a second N-type epitaxial layer 216 on the surface of the first N-type epitaxial layer 215, and performing P-type impurity implantation in the second N-type epitaxial layer 216 to form a second pair of P island structure 2102 ; the second pair...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More