A process method for chemical mechanical planarization of devices with a size below 40nm

A chemical-mechanical and process technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as circuit failure yield, affect device performance, and decrease, and achieve the goal of reducing metal loss and improving performance and yield. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

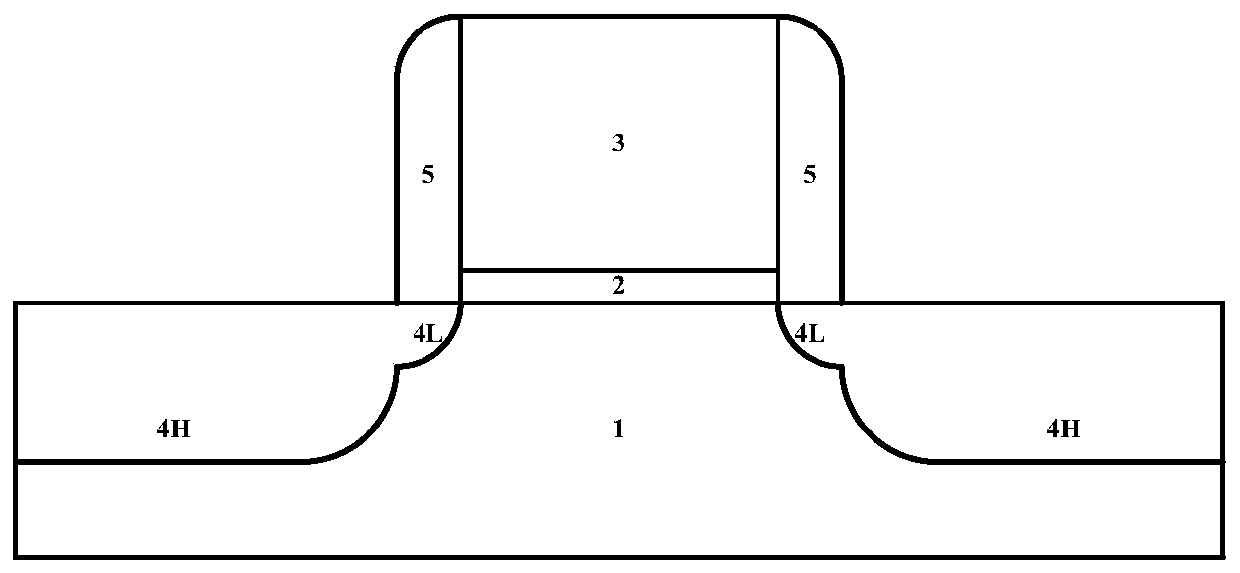

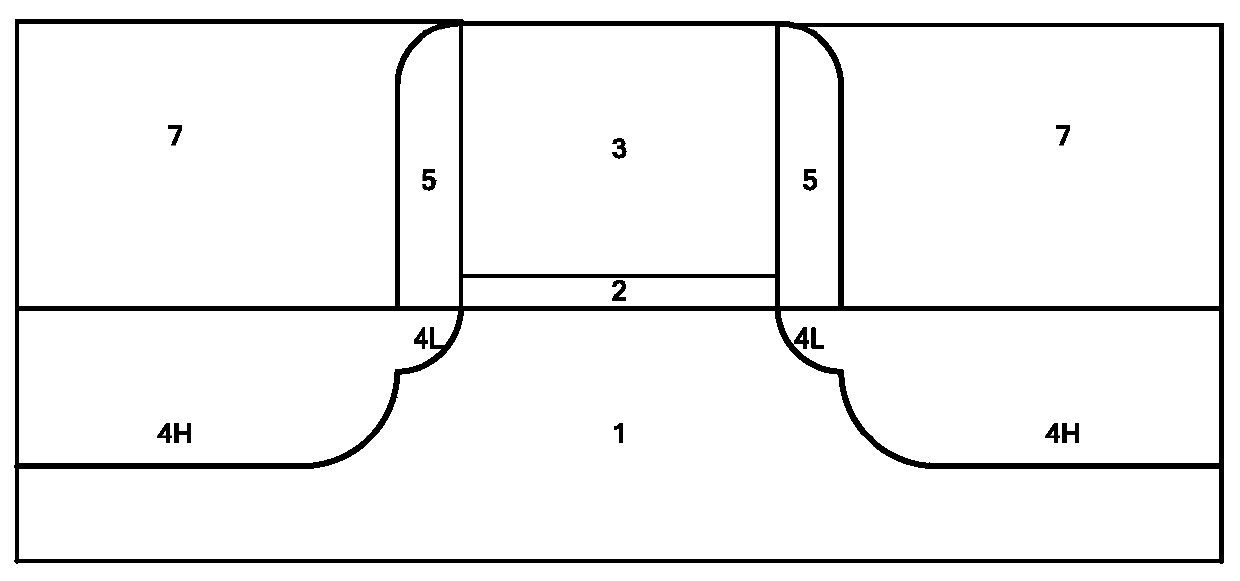

[0025] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0026] In the present invention, in the planarization process of the ALD metal tungsten, the problem that the removal rate is too high causes great loss of other layers. For this, as figure 1 Shown, the present invention proposes following technical scheme:

[0027] Metal tungsten is filled by atomic layer deposition;

[0028] A first removal process and a second removal process are performed to achieve chemical mechanical planarization of metal tungsten, wherein the pressure and rotation speed in the second removal process are respect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More