A photoelectric conversion circuit applied to mouse equipment

A technology of photoelectric conversion circuits and equipment, applied in the direction of analog-to-digital converters, etc., can solve the problems of weak output electrical signal strength, large occupied area, and high cost, and achieve the effects of enhancing photoelectric performance, reducing occupied area, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The specific implementation manner and working principle of the present invention will be further described below in conjunction with the accompanying drawings and preferred solutions.

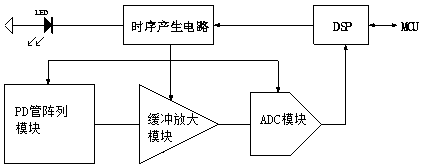

[0016] Such as figure 1 Shown is a schematic block diagram of the circuit connection peripheral structure of the present invention, which shows a schematic diagram of applying the conversion circuit of the present invention to a specific circuit. The working principle of this figure is: the photodiode array module converts the optical signal into an electrical signal, and after being amplified by the buffer amplifier module, the electrical signal is converted into a digital signal by the ADC conversion module and input to the peripheral structure DSP, and the DSP and MCU pass through the serial The bus interface receives the setting instructions of the MCU and sends the displacement information data to the MCU. At the same time, the DSP also controls the operation of the timing generati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More