clock circuit for fpga verification platform

A clock circuit and verification platform technology, applied in electrical components, automatic power control, signal generation/distribution, etc., can solve the problems of high hardware cost and labor cost, different clock frequencies, long development time, etc., to reduce hardware cost and labor costs, the effect of shortening the development time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

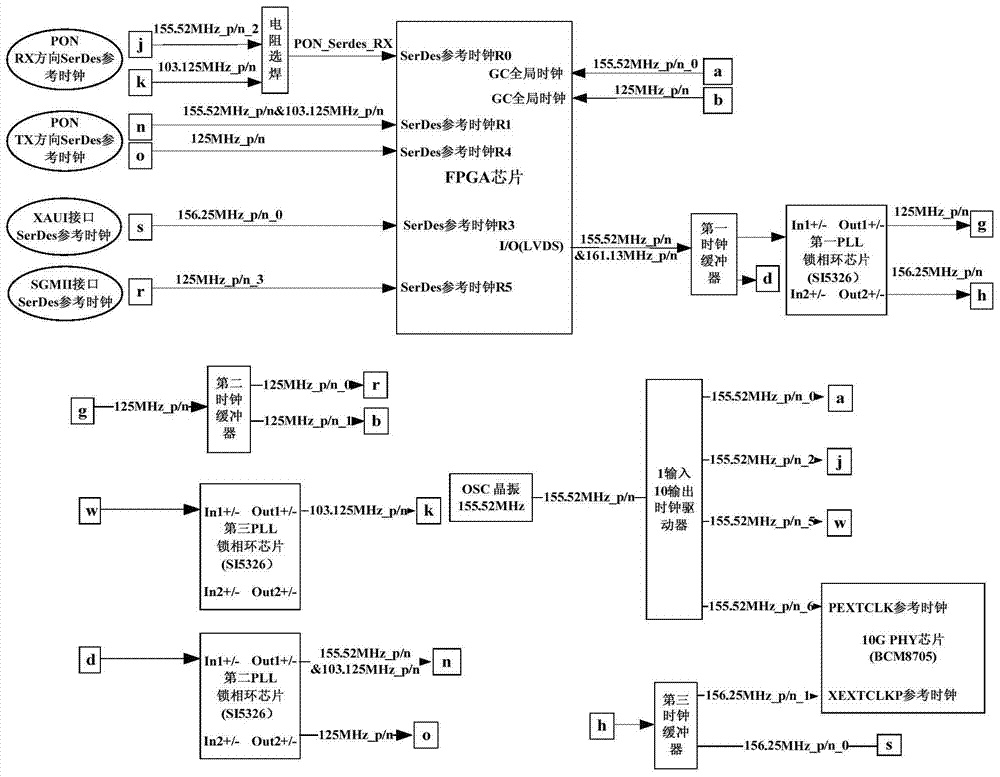

[0021] The embodiment of the present invention provides a clock circuit for an FPGA verification platform. The FPGA verification platform can verify four different types of XG-PON system, symmetrical 10G EPON system, asymmetrical 10G EPON system and GPON system only through the FPGA chip. PON system, the structural block diagram of the clock circuit is as follows figure 1 shown.

[0022] From the perspective of the uplink and downlink rates of the four PON systems listed in the background technology, the downlink rate has three different rate levels, namely 9.95328Gbit / s (XG-PON system), 10.3125Gbit / s (symmetrical 10G EPON and asymmetrical 10G EPON system) and 2.48832Gbit / s (GPON system), but there is an obvious multiple relationship between 9.95328Gbit / s and 2.48832Gbit / s, so two different SerDes (SERializer / DESerializer, serializer) in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More