Manufacturing method of optimized backside illuminated CIS pixel area deep P-type isolated well

An isolated well and back-illuminated technology, applied in the field of image sensor devices, can solve problems affecting process stability and product yield, island photoresist collapse, and inability to meet mass production process requirements, etc., to overcome ultra-high depth and width Compared with photoresist collapse, the effect of stabilizing the mass production process and improving processability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Below in conjunction with each embodiment, the technical solution of the present invention is clearly and completely set forth, but described embodiment is only the embodiment that the present invention is used for describing description and not all embodiments, based on these embodiments, this invention The solutions obtained by those skilled in the art without creative work all belong to the protection scope of the present invention.

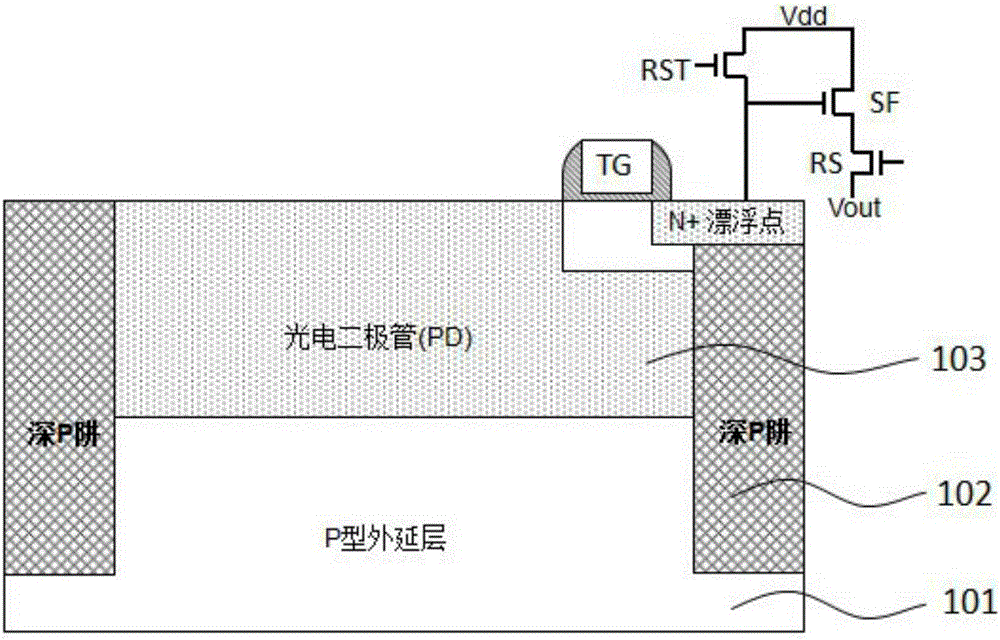

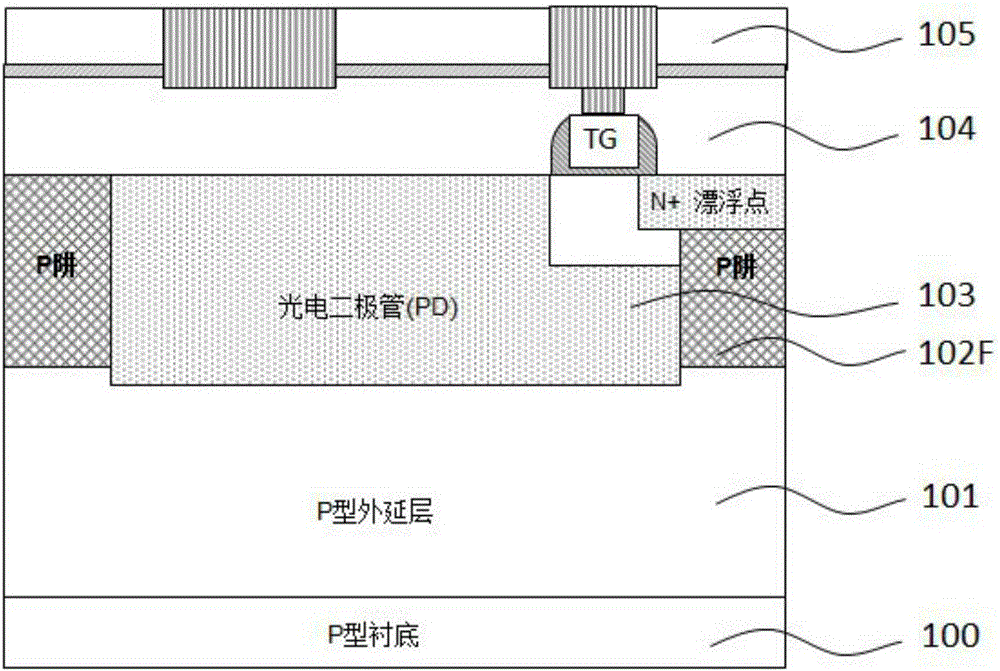

[0026] see figure 1 , showing a schematic diagram of a back-illuminated (Back-illuminated) image sensor back-end 4T pixel unit, the present invention will use this structure to explain the subsequent method. The core idea of the present invention is to disclose a method for forming an optimized deep P-type isolation well in the back-illuminated CIS pixel area. An extended P-type isolation well is formed by the ion implantation process, and a required deep P-type isolation well is jointly formed by using a bidirectional ion implantati...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Physical thickness | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Physical thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More