Thin film transistor array substrate, preparation method thereof and display device

A thin-film transistor and array substrate technology, applied in the display field, can solve problems such as ITO breakage and easy corrosion of signal lines

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

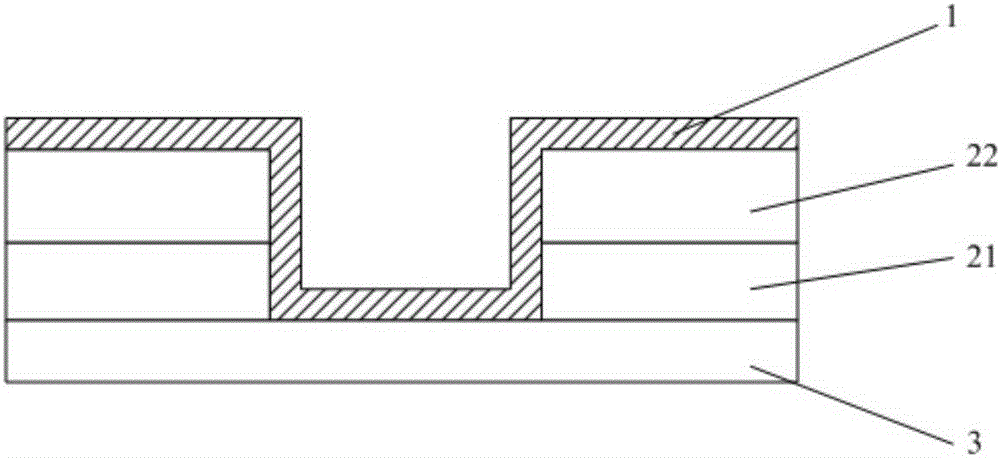

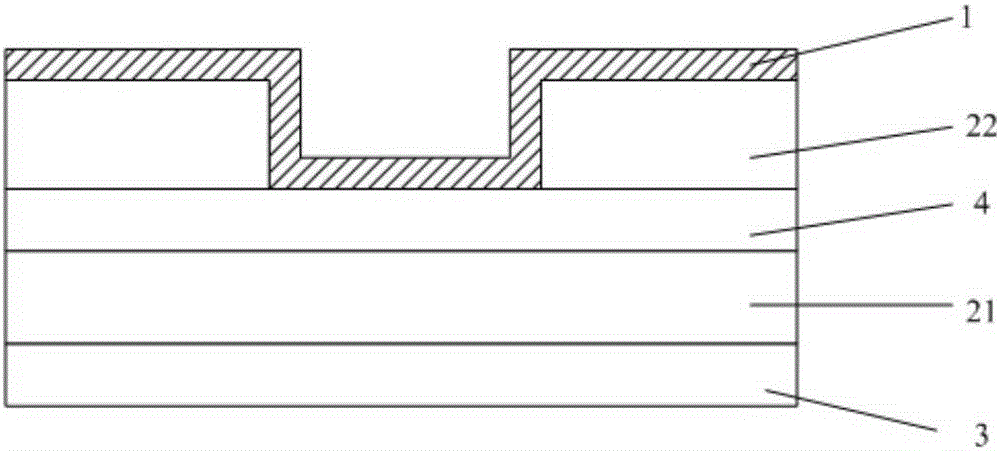

[0030] This embodiment provides a thin film transistor array substrate, including: a display area and a frame area surrounding the display area, and the frame area includes:

[0031] Substrate;

[0032] A signal line, an insulating layer, and a conductive layer are sequentially formed on the substrate, the conductive layer is connected to the signal line through a via hole in the insulating layer, and between the conductive layer and the signal line in the via hole, A corrosion-resistant conductive layer is provided.

[0033] In the TFT array substrate of this embodiment, the corrosion-resistant conductive layer is placed between the conductive layer in the via hole and the signal line to support the conductive layer, which can prevent the conductive layer from breaking and avoid abnormal display. At the same time, it can also isolate the signal line to prevent the signal line from being corroded. The thin film transistor array substrate of the present invention is suitable ...

Embodiment 2

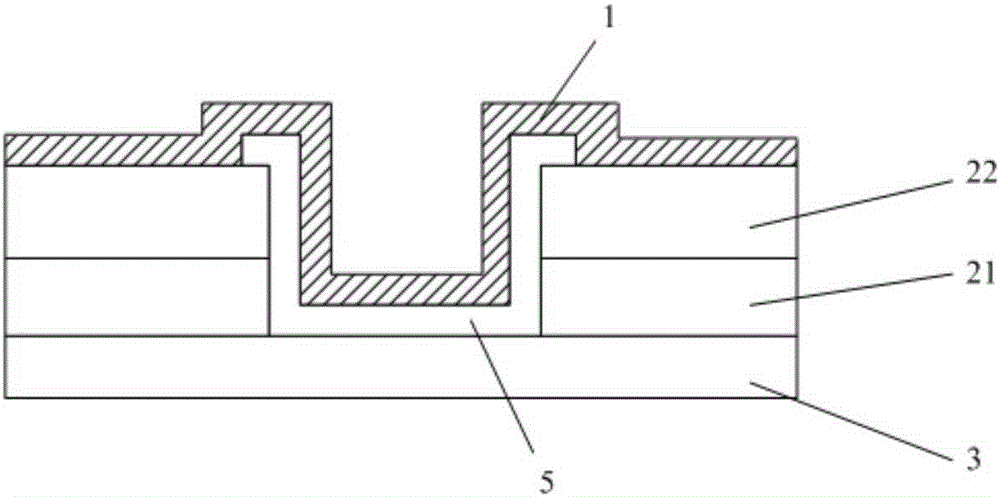

[0035] This embodiment provides a thin film transistor array substrate, including: a display area and a frame area surrounding the display area, such as image 3 , Figure 4 As shown, the border area includes:

[0036] Substrate;

[0037] A signal line, an insulating layer and a conductive layer 1 are sequentially formed on the substrate. The conductive layer 1 is connected to the signal line through a via hole in the insulating layer, and between the conductive layer 1 and the signal line in the via hole, a resistance The conductive layer 51 is etched.

[0038] In the thin film transistor array substrate of this embodiment, the corrosion-resistant conductive layer 51 is placed between the conductive layer 1 and the signal line in the via hole to support the conductive layer 1, which can prevent the conductive layer 1 from breaking and avoid abnormal display. At the same time, it can also isolate the signal line to prevent the signal line from being corroded. The thin film...

Embodiment 3

[0053] This embodiment provides a method for preparing the thin film transistor array substrate of Embodiment 2, and the specific process steps are as follows:

[0054] S1 forms the gate of the display area, and simultaneously forms the gate line 3 of the frame area;

[0055] S2 depositing the first insulating layer 21, and forming the active layer of the display area;

[0056] S3 forms a pixel electrode;

[0057] S4 forms the source and drain;

[0058] S5 forms the second insulating layer 22 and the corrosion-resistant conductive layer 51;

[0059] S6 forms the common electrode and simultaneously forms the ITO conductive layer 1 in the frame area.

[0060] The preparation method of this embodiment is simple and practical. This embodiment is only carried out with the 6Mask (gate-active layer-pixel electrode-source-drain-second insulating layer 22-pixel electrode) process commonly used in the existing planar electric field type. For illustration, it is also applicable to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More