A kind of chip arrangement resistance vacuum coating method

A technology of vacuum coating and resistance, which is applied in the direction of vacuum evaporation coating, resistors, resistance manufacturing, etc. It can solve the problem that the resistance grooves arranged in the array are easy to be sputtered, and achieve the effect of improving product quality and improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Embodiment 1: a kind of wafer arrangement resistance vacuum coating method, it comprises the following steps:

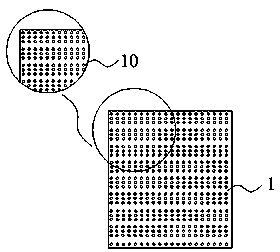

[0045] Substrate preparation: take a substrate 1, a plurality of holes 10 are evenly distributed in a matrix on the substrate 1, wherein every three holes are vertically arranged as a group;

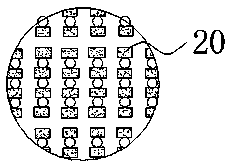

[0046] Step C2: print the conductor 20 on the back side of the substrate, see attached figure 2 ;

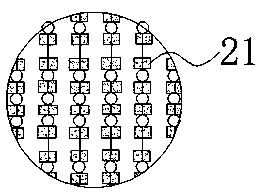

[0047] Step C1: Print conductor 21 on the front side of the substrate, see attached image 3 ;

[0048] Step RS: print resistance 22 on the front side of the substrate, the position of resistance 22 is between two printed conductors adjacent to the front side of the substrate, see Figure 4 ;

[0049] Step G1: After the step RS is finished, print the resistance layer protection layer 23 on the substrate 1, and the resistance layer protection layer 23 covers the resistance 22 printed in the step RS, see Figure 5 ;

Embodiment 2

[0057] Embodiment 2: The difference between this embodiment and Embodiment 1 is that in this embodiment, the printing thickness when printing the conductor in step C2 is 31±10 μm; the printing thickness when printing the conductor in step C1 is 25±10 μm; step RS The printing thickness of the medium resistance is 20±10 μm; the printing thickness of the resistive protective layer in step G1 is 20±10 μm; the thickness of the printed laser protective layer in step G2 is 20±10 μm.

Embodiment 3

[0058] Embodiment 3: The difference between this embodiment and Embodiment 1 is that in this embodiment, during the silver termination process, the impedance of the coating on both sides of each resistance unit: ≦65Ω; during the electroplating process, the plating on the surface of each resistance unit The thickness of the nickel layer is between 5.0-6.0 μm; the thickness of the galvanized layer on the surface of each resistance unit is between 7.0-8.0 μm.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More