A through-silicon via structure based on a pn junction and its manufacturing method

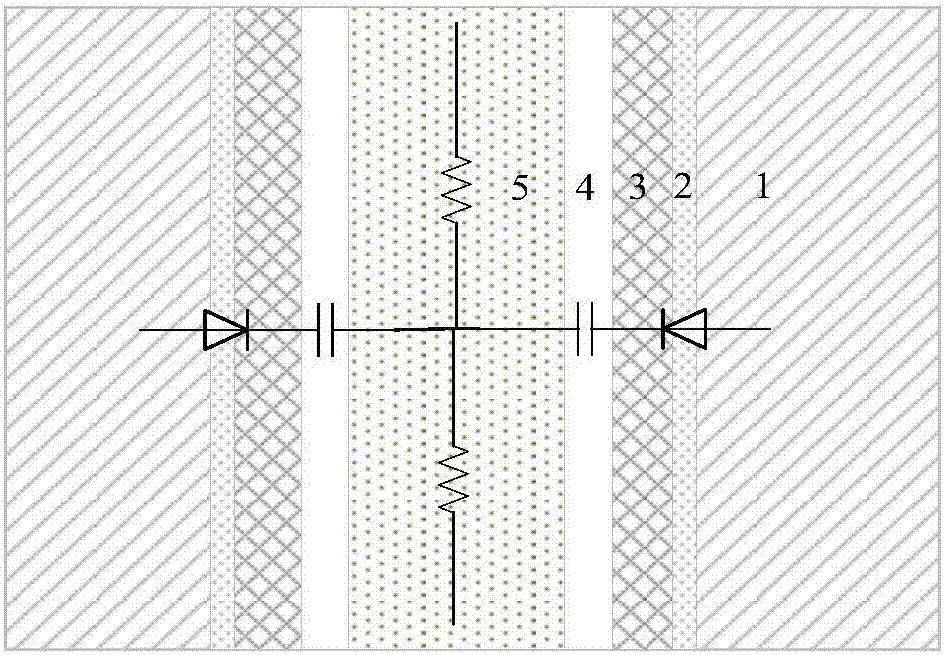

A manufacturing method and a technology of through-silicon vias, which are applied in semiconductor/solid-state device manufacturing, electrical components, and electrical solid-state devices, can solve problems such as troublesome use and grounding, reduce the use of metals, improve thermomechanical reliability, and high Effects of High Frequency Signal Integrity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

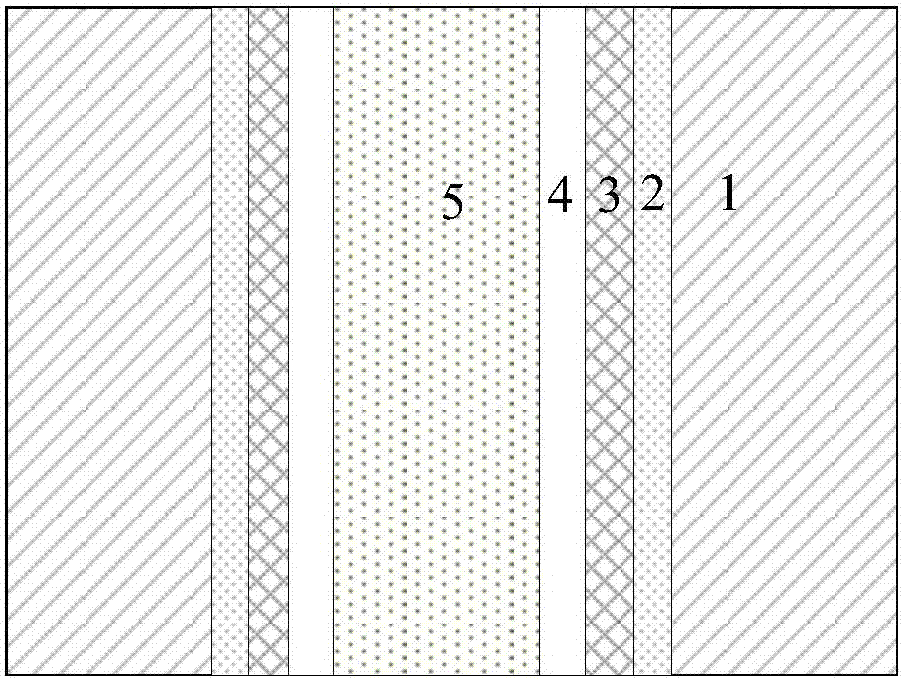

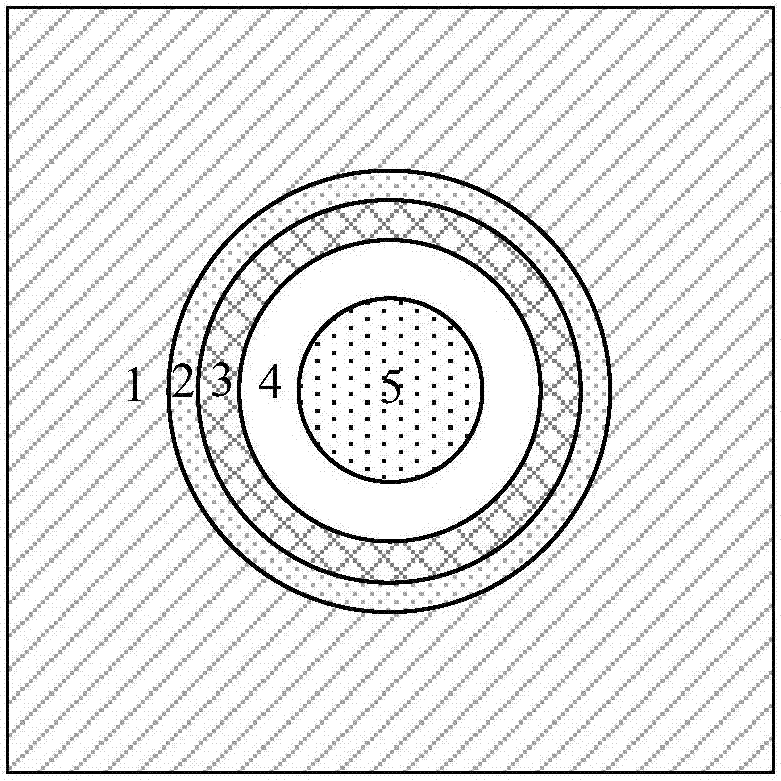

[0058] Step 1, selecting a P-type doped silicon substrate as the substrate 1;

[0059] Step 2, using reactive ion method to etch a through hole penetrating through the upper and lower surfaces of the substrate 1 on the substrate 1, the radius of the through hole is 2.6 μm;

[0060] Step 3, preparing an N-type doped layer 3 on the inner surface of the through hole formed by etching in step 2;

[0061] Specifically follow the steps below:

[0062] Step 3.1, using a constant surface source diffusion method to deposit impurity atoms on the inner surface of the through hole formed by etching in step 2;

[0063] Step 3.2: Put the substrate 1 deposited with impurity atoms in step 3.1 into a horizontal diffusion furnace by means of limited surface source diffusion. The temperature of the horizontal diffusion furnace is 950° C. The substrate 1 is diffused to form an N-type doped layer 3, and the surface concentration and doping depth of the N-type doped layer 3 are 0.5 μm.

[0064] ...

Embodiment 2

[0068] Step 1, selecting a P-type doped silicon substrate as the substrate 1;

[0069] Step 2, using reactive ion method to etch a through hole penetrating through the upper and lower surfaces of the substrate 1 on the substrate 1, the radius of the through hole is 4 μm;

[0070] Step 3, preparing an N-type doped layer 3 on the inner surface of the through hole formed by etching in step 2;

[0071] Specifically follow the steps below:

[0072] Step 3.1, using a constant surface source diffusion method to deposit impurity atoms on the inner surface of the through hole formed by etching in step 2;

[0073] Step 3.2: Put the substrate 1 on which impurity atoms have been deposited in step 3.1 into a horizontal diffusion furnace by means of limited surface source diffusion. The temperature of the horizontal diffusion furnace is 1000° C. The substrate 1 is diffused to form an N-type doped layer 3, and the surface concentration and doping depth of the N-type doped layer 3 are 1 μm....

Embodiment 3

[0078] Step 1, selecting a P-type doped silicon substrate as the substrate 1;

[0079] Step 2, using reactive ion method to etch a through hole penetrating through the upper and lower surfaces of the substrate 1 on the substrate 1, the radius of the through hole is 6 μm;

[0080] Step 3, preparing an N-type doped layer 3 on the inner surface of the through hole formed by etching in step 2;

[0081] Specifically follow the steps below:

[0082] Step 3.1, using a constant surface source diffusion method to deposit impurity atoms on the inner surface of the through hole formed by etching in step 2;

[0083] Step 3.2: Put the substrate 1 on which impurity atoms have been deposited in step 3.1 into a horizontal diffusion furnace by means of limited surface source diffusion. The temperature of the horizontal diffusion furnace is 1050° C. The substrate 1 is diffused to form an N-type doped layer 3, and the surface concentration and doping depth of the N-type doped layer 3 are 1.5 μ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More