Memory reading method and digital memory device

A technology for memory and data reading, which is applied in static memory, read-only memory, information storage, etc., and can solve problems such as difficult to support serial or non-gate flash memory high-speed code mapping applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

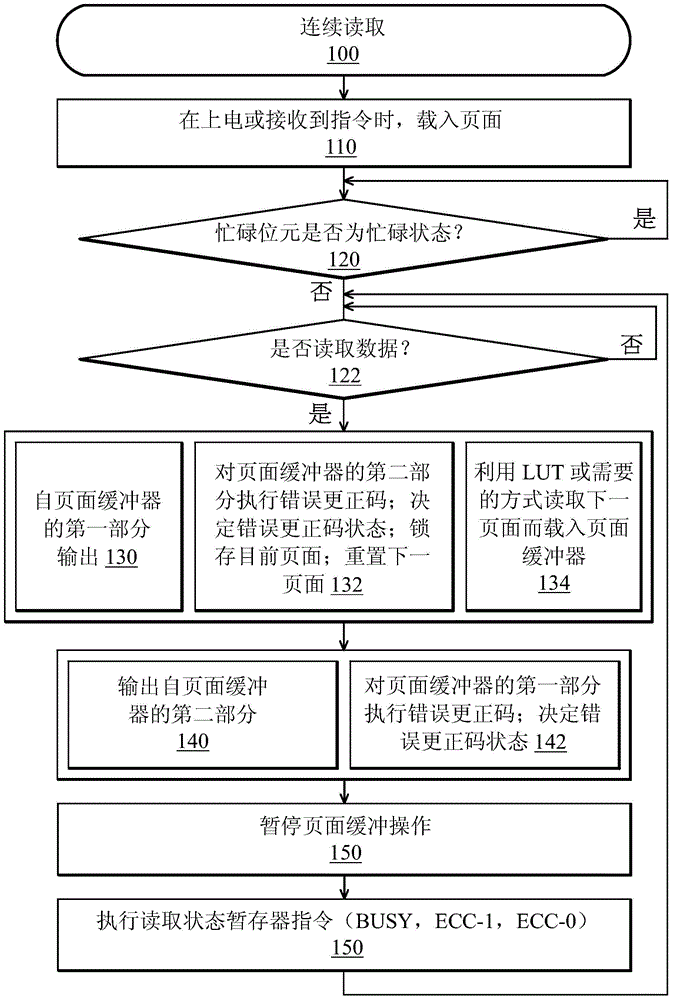

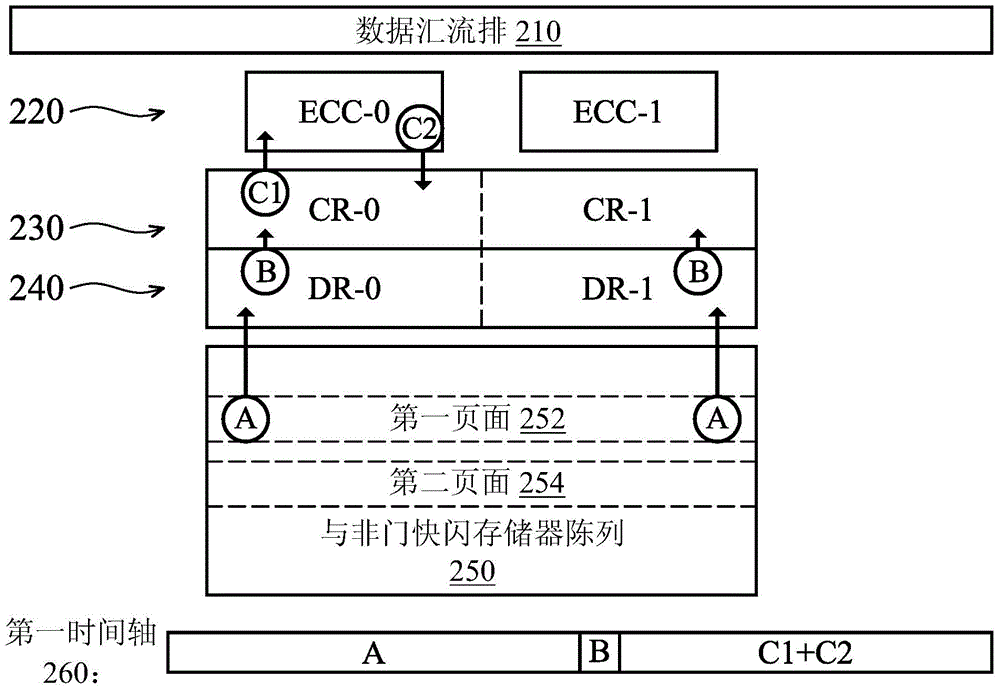

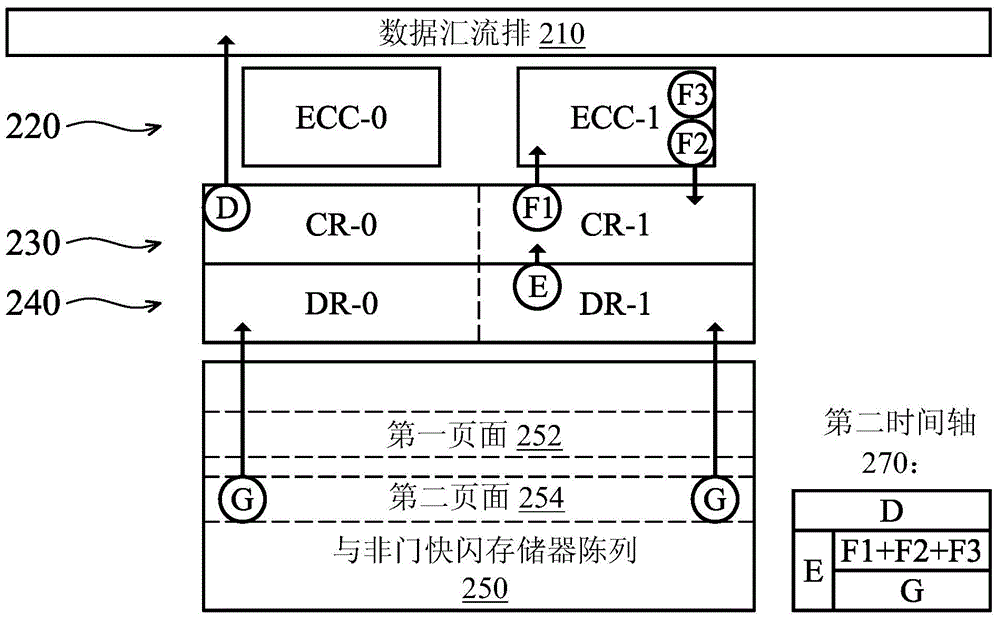

[0071] NAND memory devices can be fabricated with many characteristics compatible with NOR memory devices, including (1) multiple input / output (I / O) serial peripheral interface (SPI) / quick path interconnect (QPI) interfaces; (2) Package type with less number of pins (8*6mm with a density of 256Mb or higher), for example, WSON with 8 contacts, SOIC with 16 pins and BGA type package with 24 balls, with the use of The flexibility of large packages (such as VBGA-63 commonly used in general parallel or general serial NAND flash memory); (3) high clock frequency operation (such as 104MHz) versus high transfer rate (such as 50MHz / second); ( 4) Continuous reads across page boundaries with error correction code processing for fast code-mapping applications without latency; Bad block management (bad block management), logically continuous marked memory; and (6) through the value set by the user or the manufacturer, to determine the output start address is logic 0 or the user in the memo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More