Chip structure for effectively increasing PN junction area and manufacturing method thereof

A chip structure and PN junction technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of increasing chip cost and increasing the area of PN junctions, etc., and achieve the effect of increasing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

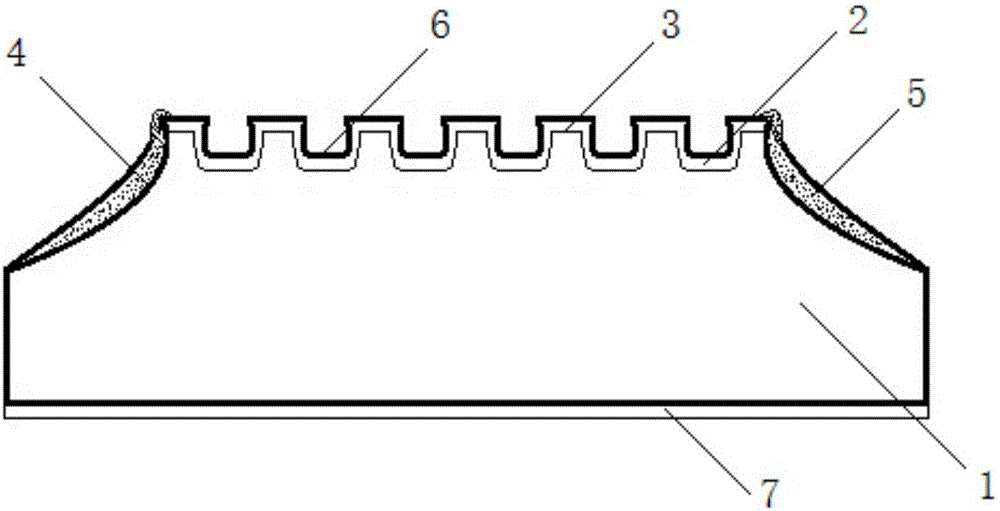

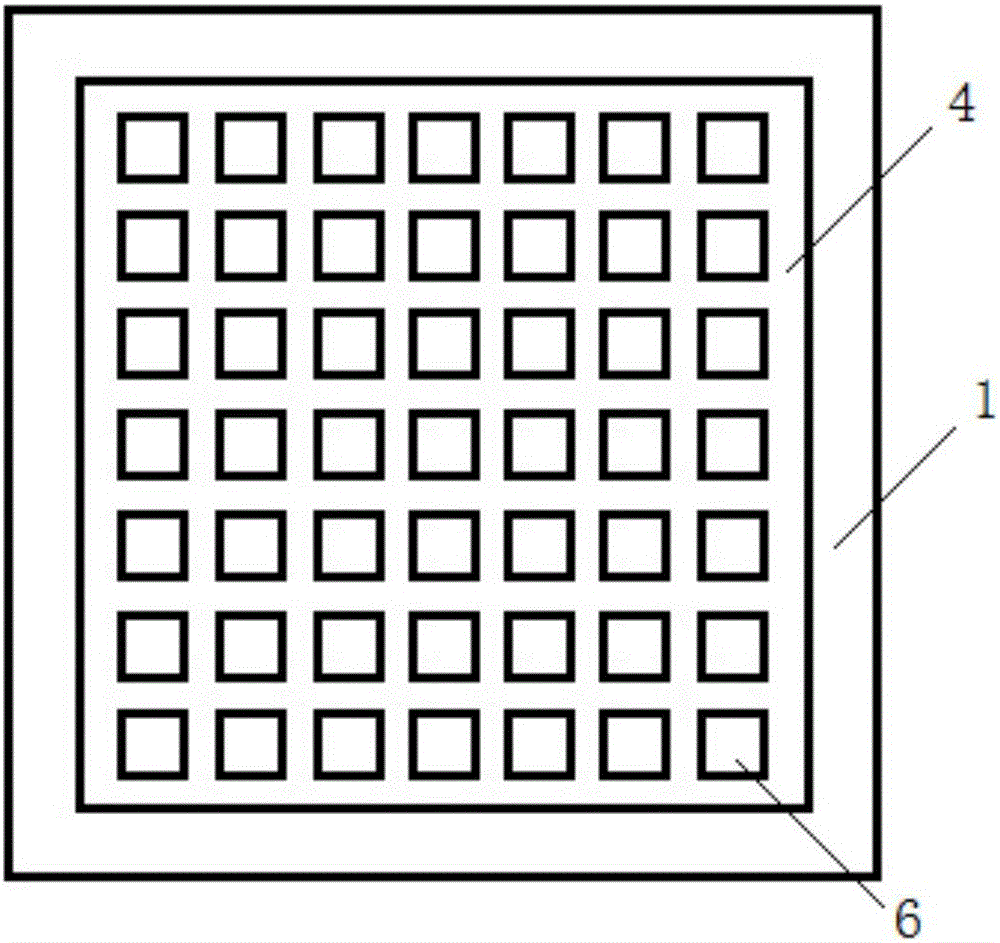

[0033] Embodiment 1: as figure 1 As shown, a chip structure that effectively increases the area of the PN junction includes a chip body, the chip body includes a substrate layer 1, and one of the surfaces of the substrate layer 1 is provided with several equally spaced pits 6, and the cross-section of the pits 6 shaped like Figure 3 to Figure 6 As shown, it can be square, circular, hexagonal or annular, etc., and any pattern structure that can form the shape of the PN junction 3 in this embodiment is included; The heavily doped layer 2 with the opposite conductivity type forms a PN junction 3 at the intersection between the substrate layer 1 and the heavily doped layer 2, and the PN junction 3 is formed by a number of U-shaped curved surface junctions connected front and back, in which the U-shaped The middle part of the surface knot is a plane knot. There is a boss 4 in the middle of the side of the chip body with the pit 6, the PN junction is exposed on the side of the...

Embodiment 2

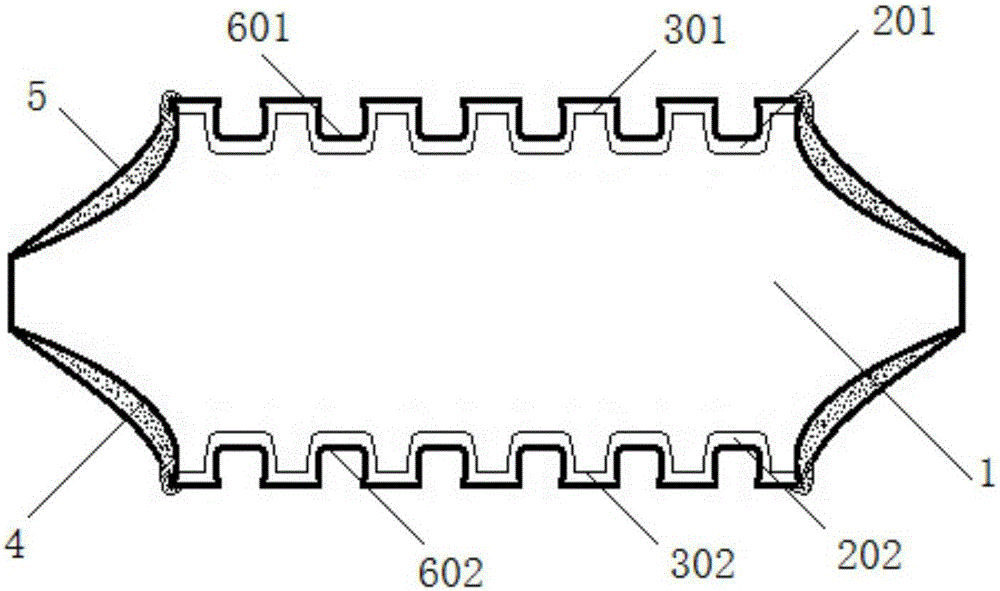

[0039] Embodiment 2: as figure 2 As shown, a chip structure that effectively increases the area of the PN junction includes a chip body, the chip body includes a substrate layer 1, the upper surface of the substrate layer 1 is provided with a number of equally spaced pits 601, and the lower surface of the substrate layer 1 is also There are several equally spaced pits 602 symmetrically. The pits 601 and 602 have the same shape, and their cross-sectional shapes are as follows: Figure 3 to Figure 6 As shown, it can be a square, a circle, a hexagon, or a ring, etc., and any graphic structure that can form the shape of the PN junction in this embodiment is included. The upper surface of the chip body is doped to form a heavily doped layer 201 of the opposite conductivity type to the substrate layer 1, and the first PN junction 301 is formed at the intersection between the substrate layer 1 and the heavily doped layer 201; on the lower surface of the chip body doping to form a...

Embodiment 3

[0045] Embodiment 3: as Figure 7As shown, a chip structure that effectively increases the area of the PN junction includes a chip body, the chip body includes a substrate layer 1, and one of the surfaces of the substrate layer 1 is doped to form a heavily doped layer 2 of a conductivity type opposite to that of the substrate layer 1, The intersection between the substrate layer 1 and the heavily doped layer 2 forms a PN junction 3, and the PN junction 3 is formed by connecting a number of U-shaped curved surface junctions front and back, wherein the middle part of the U-shaped curved surface junction is a planar junction, and the PN junction 3 is exposed on the surface where the heavily doped layer 2 is located, and the exposed part of the PN junction 3 is covered with a passivation layer 5. The passivation layer 5 is used to encapsulate the exposed PN junction 3 and isolate it from the outside world. The upper and lower surfaces of the chip body are uniform Covered with a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More