DDR (Double Data Rate) time sequence and delay skew simulation evaluation method based on lookup table

A look-up table and timing technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems that cannot be realized at the same time, achieve the effects of shortening the progress and complexity, facilitating iterative optimization, and ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

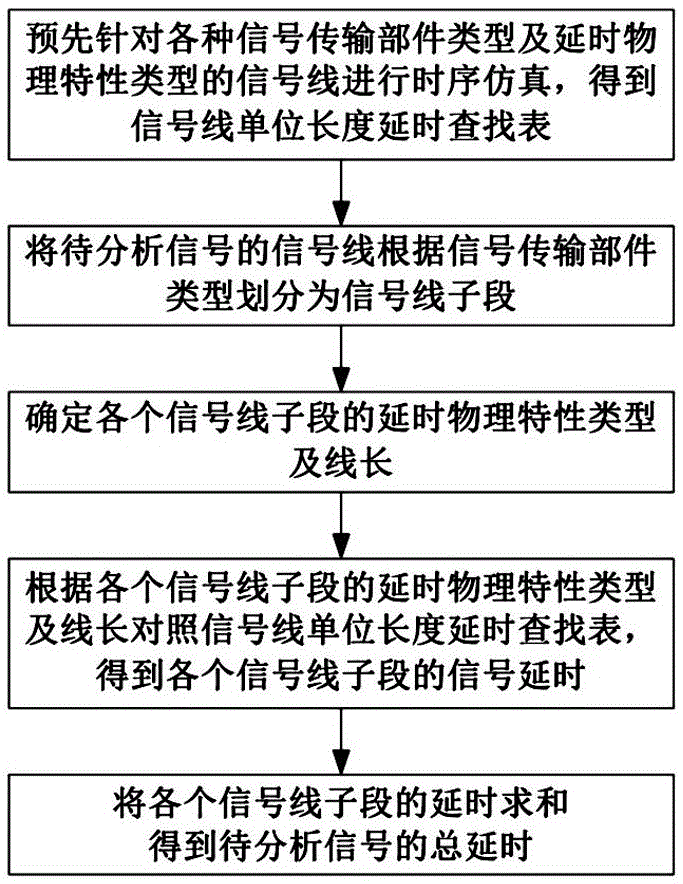

[0035] Such as figure 1 As shown, the steps of the DDR timing simulation evaluation method based on the lookup table in this embodiment include:

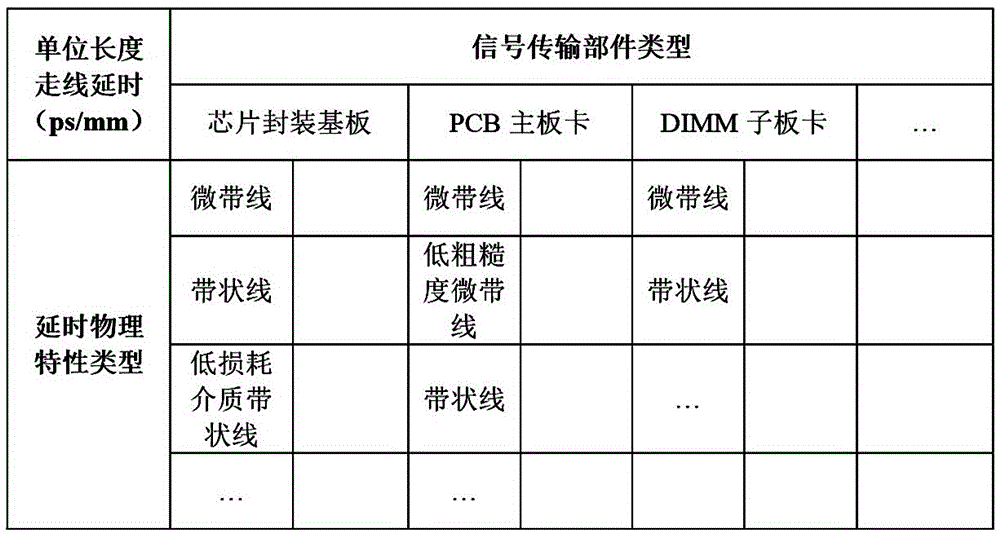

[0036] 1) Timing simulation is carried out in advance for the signal lines of various signal transmission component types, and the signal line unit length delay lookup tables of various signal transmission component types are obtained. The table items of the signal line unit length delay lookup table include the specified The type of signal transmission component corresponds to the type of delay physical characteristics, and the corresponding relationship between the unit length trace delay;

[0037] 2) Divide the signal line of the signal to be analyzed into signal line sub-sections according to the type of signal transmission components, and determine the delay physical characteristic type and line length of each signal line sub-section;

[0038] 3) According to the delay physical characteristic type and line length of each sign...

Embodiment 2

[0053] Different from the first embodiment, this embodiment is based on the first embodiment, and further applies the look-up table-based DDR timing simulation evaluation method of the first embodiment to the calculation of the delay skew of two signals.

[0054] In this embodiment, the DDR timing delay skew simulation evaluation method based on the lookup table, the steps include: I) adopting the aforementioned DDR timing simulation evaluation method based on the lookup table of the present invention, respectively obtaining the total delay of the two signals to be analyzed; II) Subtract the total delay of the two signals to be analyzed to obtain the delay skew (in ps) between the two signals to be analyzed.

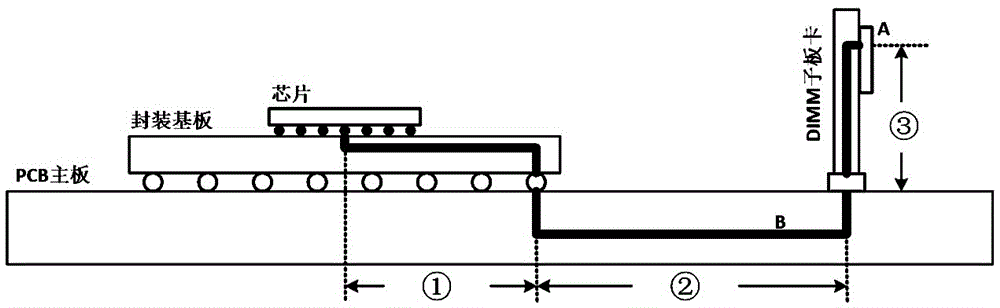

[0055] In addition, in the method of this embodiment, the impact of the three signal transmission components on the signal delay of the connector, the chip solder ball, and the intermediate board between the PCB main board and the DIMM daughter board on the signal transmi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More