Thin film transistor, array substrate, display panel and display device

A technology of thin film transistors and array substrates, applied in the display field, can solve problems such as easy disconnection, and achieve the effects of reducing the occupied area, increasing the aperture ratio, and increasing the aspect ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0038] Example 1: The above thin film transistor provided by the embodiment of the present invention is applied to a bottom gate thin film transistor.

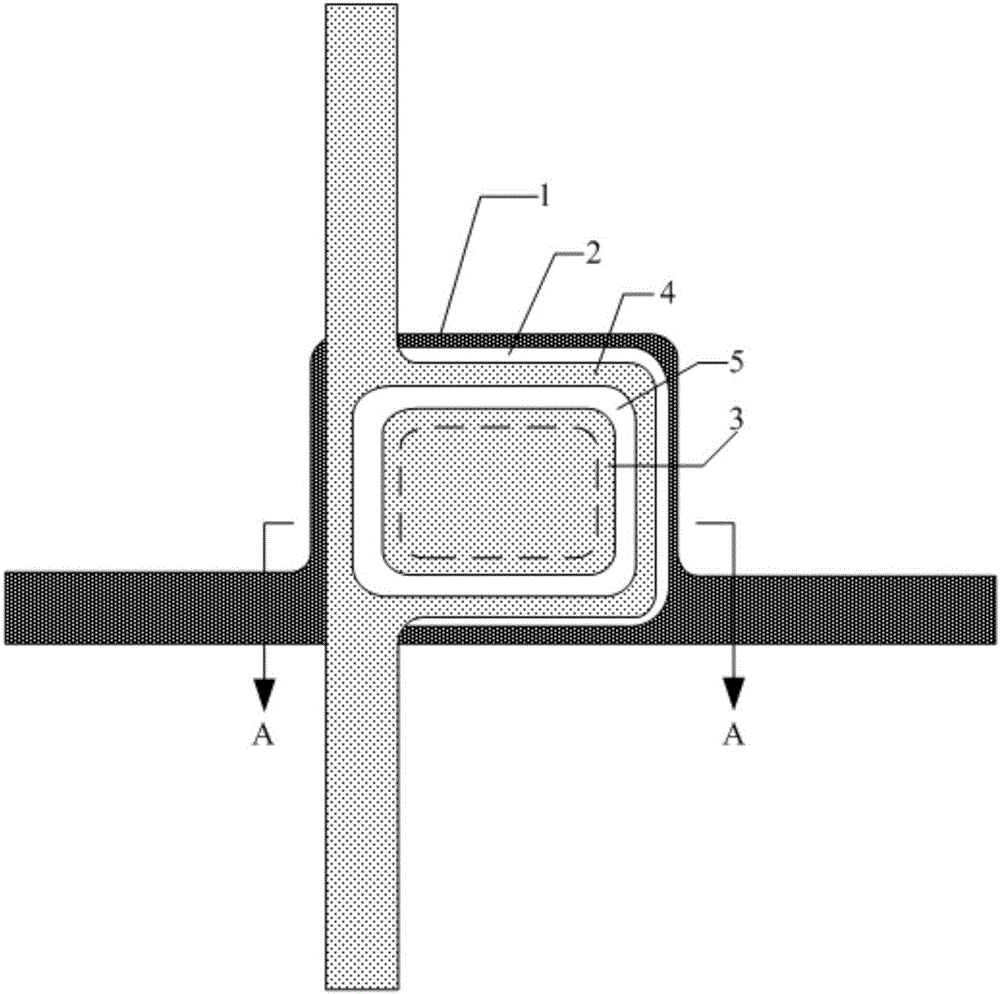

[0039] In specific implementation, in the above-mentioned thin film transistor provided by the embodiment of the present invention, such as Figure 4 as shown, Figure 4 for image 3 In the cross-sectional view along the AA direction, the active layer 2 is located above the gate electrode 1 ; the source electrode 3 and the drain electrode 4 are located above the active layer 2 .

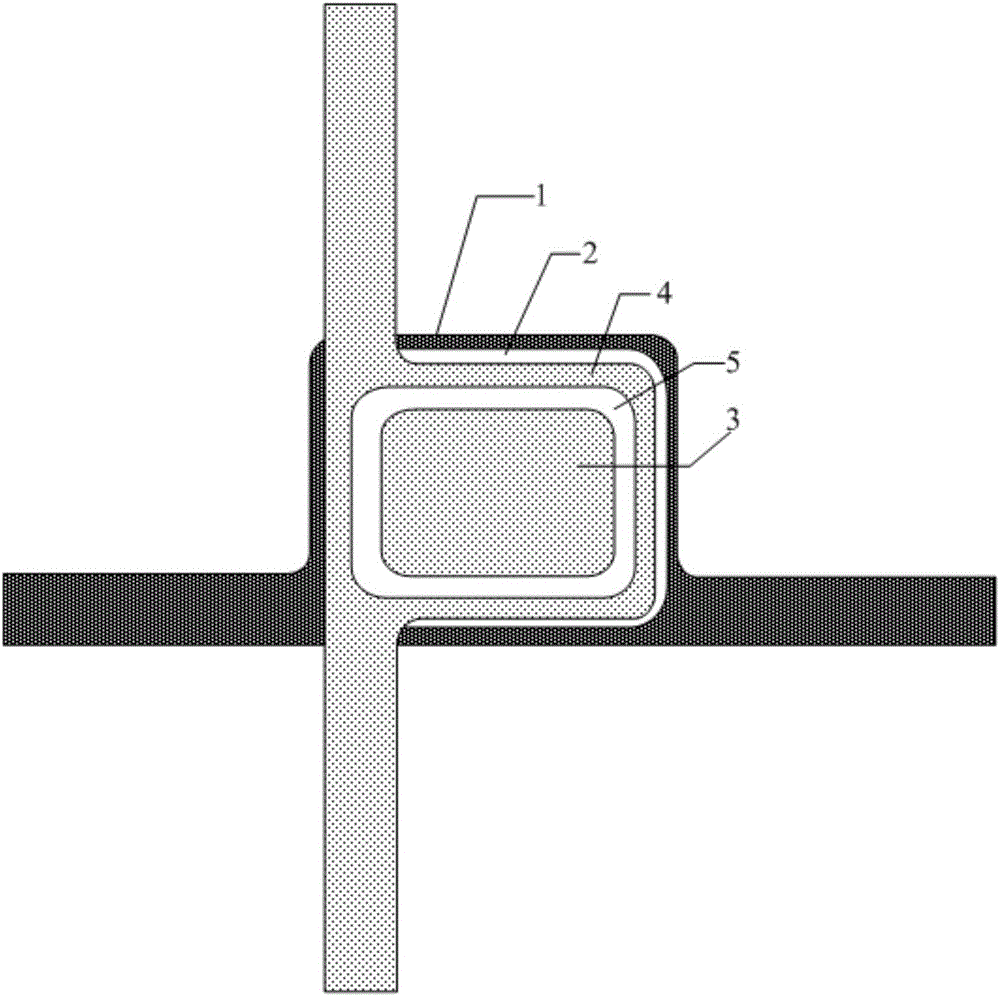

[0040] Preferably, in the above-mentioned thin film transistor provided by the embodiment of the present invention, such as image 3As shown, the orthographic projection of the channel 5 on the gate electrode 1 can be set in the area where the gate electrode 1 is located, that is, the area of the hollowed out part of the gate electrode 1 is smaller than or equal to the area of the source electrode 3, so that the gate electrode 1 can block the c...

example 2

[0042] Example 2: The above-mentioned thin film transistor provided by the embodiment of the present invention is applied to a top-gate thin film transistor.

[0043] In specific implementation, in the above-mentioned thin film transistor provided by the embodiment of the present invention, such as Figure 5 As shown, the active layer 2 is located above the source electrode 3 and the drain electrode 4 ; the gate electrode 1 is located above the active layer 2 .

[0044] It should be noted that the specific implementation of Example 2 of the present invention is similar to the implementation of Example 1 of the present invention, and repeated descriptions will not be repeated.

[0045] Based on the same inventive concept, an embodiment of the present invention further provides an array substrate, including: the above-mentioned thin film transistor provided by the embodiment of the present invention. For the implementation of the array substrate, reference may be made to the ab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More