Pico-second superfast electrical property testing system for semiconductor device

A technology of electrical characteristics and semiconductors, which is applied in the field of electrical parameter extraction of semiconductor devices, can solve problems such as inability to fully reflect the transport of carriers and defects, and achieve the effect of ensuring integrity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

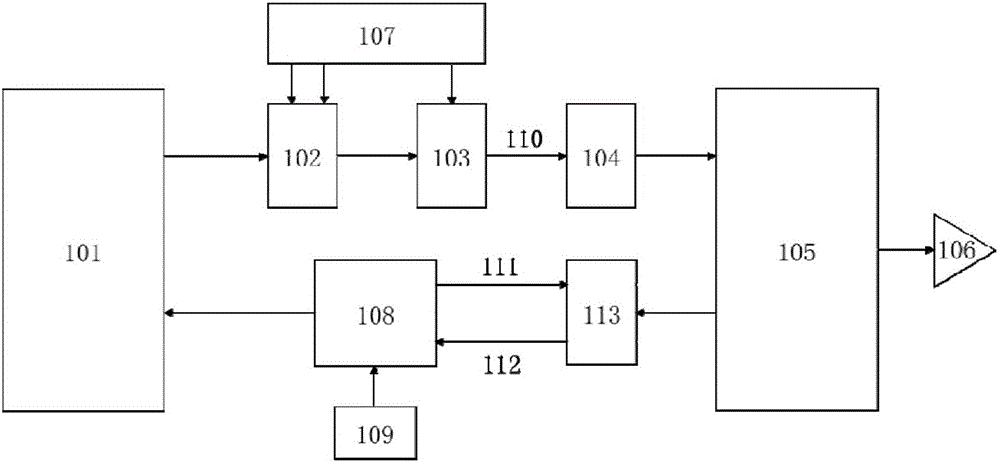

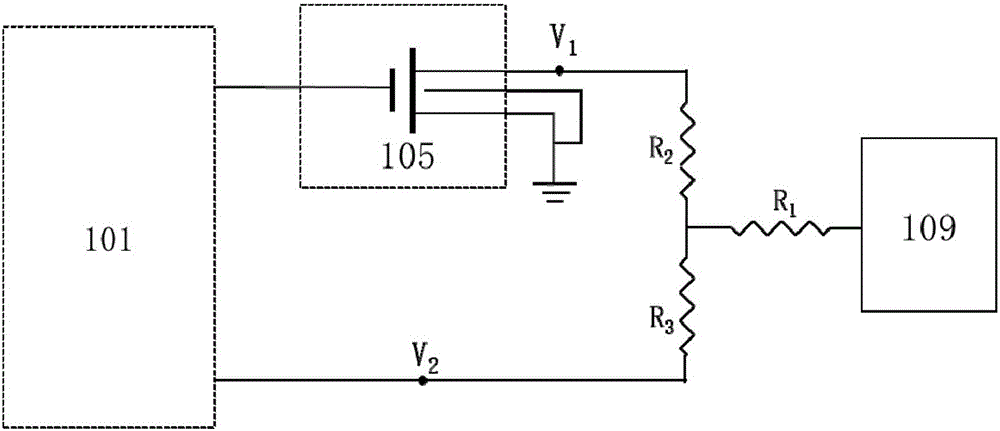

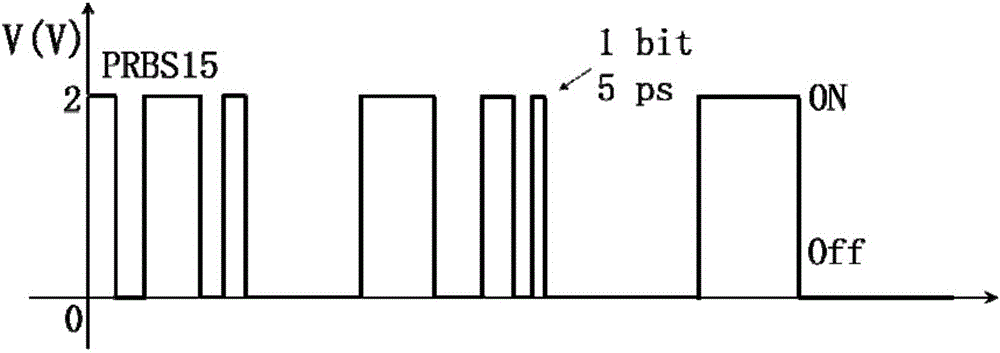

[0019] Such as figure 1 As shown, this embodiment is a picosecond-level ultra-fast electrical characteristic testing system applied to semiconductor devices, including a waveform processor 101, a broadband voltage amplifier 102, a broadband voltage bias device 103, and a broadband pick-up tee device 108 , the first microwave probe 104 , and the second microwave probe 113 . The waveform processor 101 generates a voltage pulse waveform whose rising edge and falling edge are less than 100pS or a voltage signal 110 of a pseudo-random binary code sequence voltage waveform, which is sequentially transmitted from the output channel to the broadband voltage amplifier 102 and the broadband voltage biaser 103 , the gate voltage signal 110 is loaded on the gate of the MOSFET transistor 105 to be tested through the first microw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More