Array substrate and preparation method thereof, display panel, and display device

A technology for array substrates and display panels, applied in static indicators, semiconductor/solid-state device manufacturing, instruments, etc., can solve the problems of reducing the side frame of the gate drive, reducing the side frame of the gateIC, etc., to reduce the difficulty of drilling , reduce complexity, reduce the effect of width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0045] The invention also discloses a method for preparing an array substrate, the method comprising:

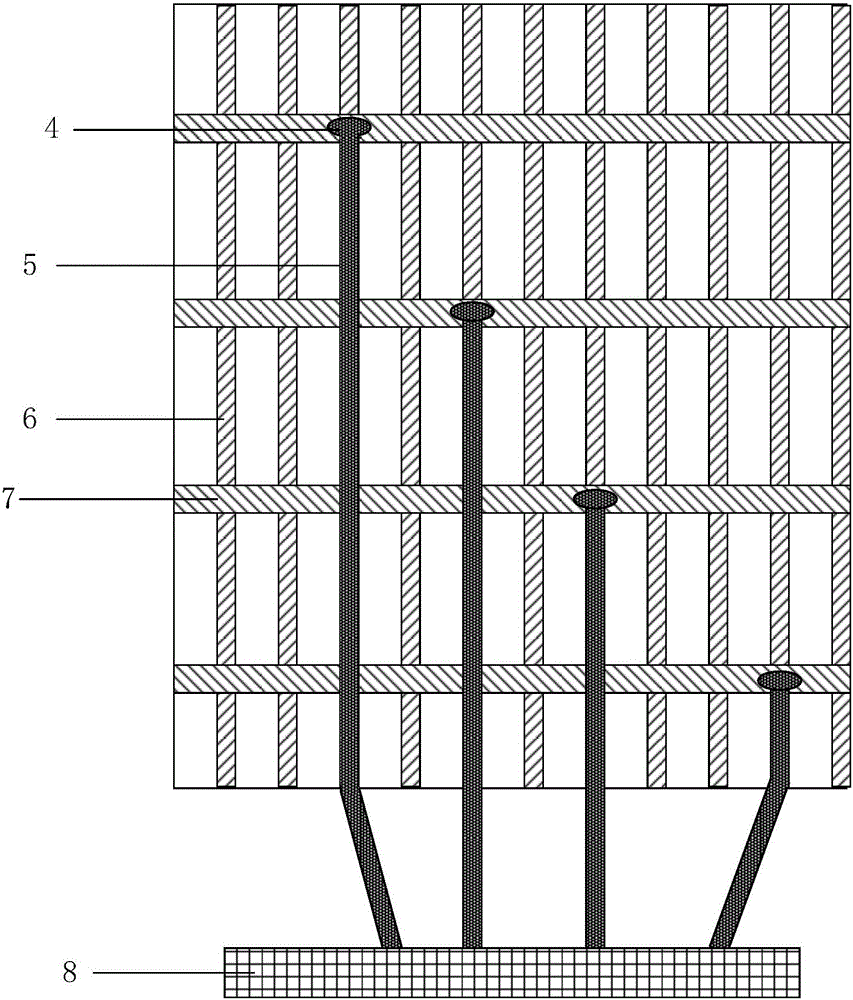

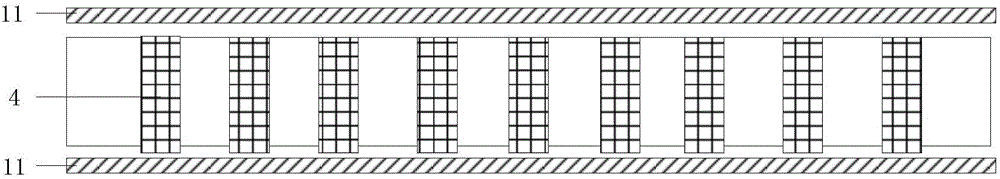

[0046] S1. Form via holes on a substrate with gate lines, data lines, and gate fan-out lines formed on one side; wherein the via holes are arranged in the projection area of the gate lines on the substrate;

[0047] S2. Form a gate fan-out line on the side of the substrate that is away from the gate line, so that the gate fan-out line is connected to the gate of the array substrate through a via hole; the gate fan-out line is routed along the black matrix projection area and extends to the driver binding area.

[0048] In the above method, the gate fan-out line is arranged on the side of the substrate that is away from the gate line, and the line is routed along the projection area of the black matrix and extended to the driving bonding area, so that the gate fan-out line does not go along the side of the array substrate, thereby reducing the The width of the gate drivi...

Embodiment 1

[0059] The method of the present embodiment comprises the following steps:

[0060] S11. Manufacturing openings on the TFT glass substrate by one etching or laser drilling method, the openings are arranged in the first black matrix projection area gate BM corresponding to the grid line area of the substrate and the second black matrix corresponding to the data line area. Intersection of matrix projection area Source BM. The etching method in this step may be Dry Etch, Wet Etch or RIE etc.

[0061] S12. Deposit a conductive material in the opening by means of electroplating, physical vapor deposition PVD or chemical vapor deposition CVD. The conductive material can be metal, conductive semiconductor or conductive plastic.

[0062] S13 , removing the protruding conductive material through chemical mechanical polishing (CMP) to make the back surface of the TFT glass substrate flat.

[0063] S14. Manufacture a gate fanout line gatefanout on the back of the TFT glass substrate ...

Embodiment 2

[0073] The method of the present embodiment comprises the following steps:

[0074] S21. Making openings on the TFT glass by etching twice or laser drilling, the openings are at the junction of the gate BM and the Source BM. The etching method in this step may be Dry Etch, Wet Etch or RIE etc.

[0075] S22. Deposit a conductive material in the opening by means of electroplating, PVD, CVD, etc. The conductive material can be metal, conductive semiconductor or conductive plastic.

[0076] S23 , removing the protruding conductive material by CMP, so that the back surface of the TFT glass substrate is flat.

[0077] S24. Manufacture a gate fanout on the back of the TFT glass substrate by photolithography→thin film deposition→etching. The fanout line is along the BM projection direction and communicates with the conductive material of the opening.

[0078] S25 , depositing a protective layer for gate fanout.

[0079] The difference between the method of this embodiment and the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More