Epitaxial wafer manufacturing method and epitaxial wafer

A technology of epitaxial wafers and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as uncaptured gettering regions, poor crystallinity of wafer surfaces, and epitaxial layer defects, etc., to achieve excellent absorption effect of suppressing the formation of epitaxial defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

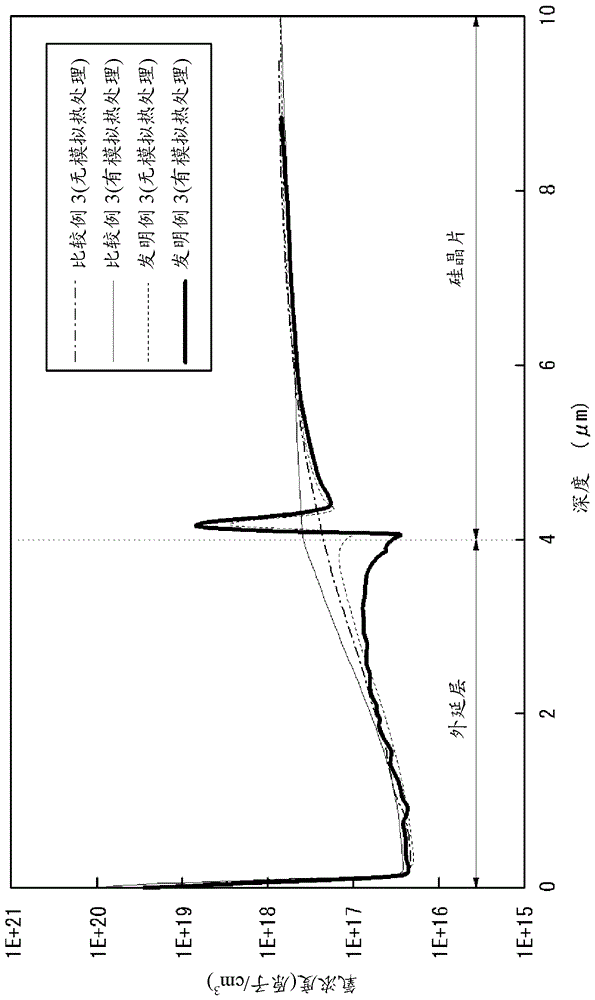

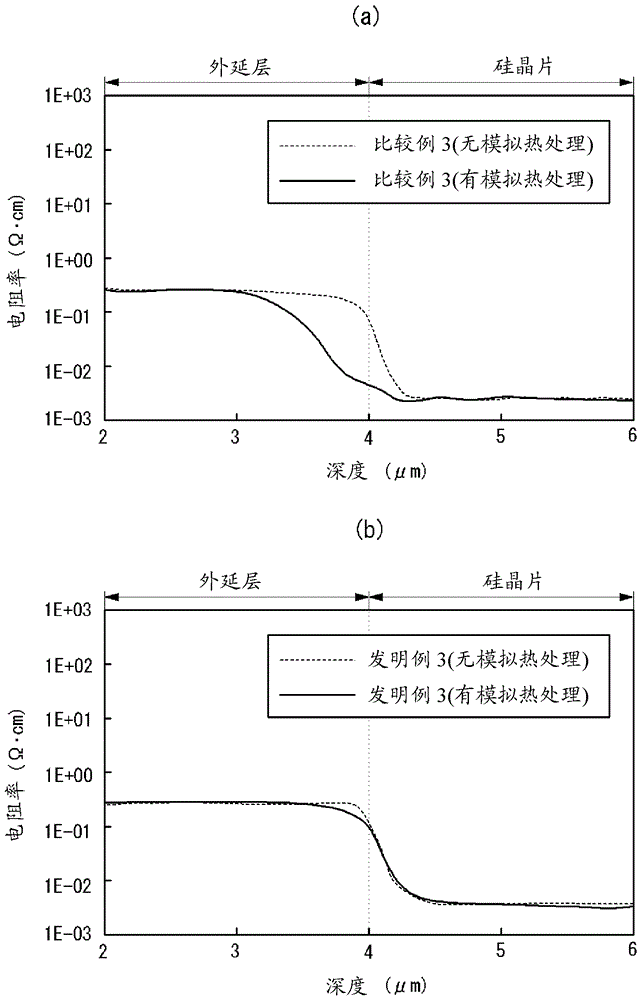

[0069] (Invention Example 1-Invention Example 3)

[0070] Examples of the present invention will be described below.

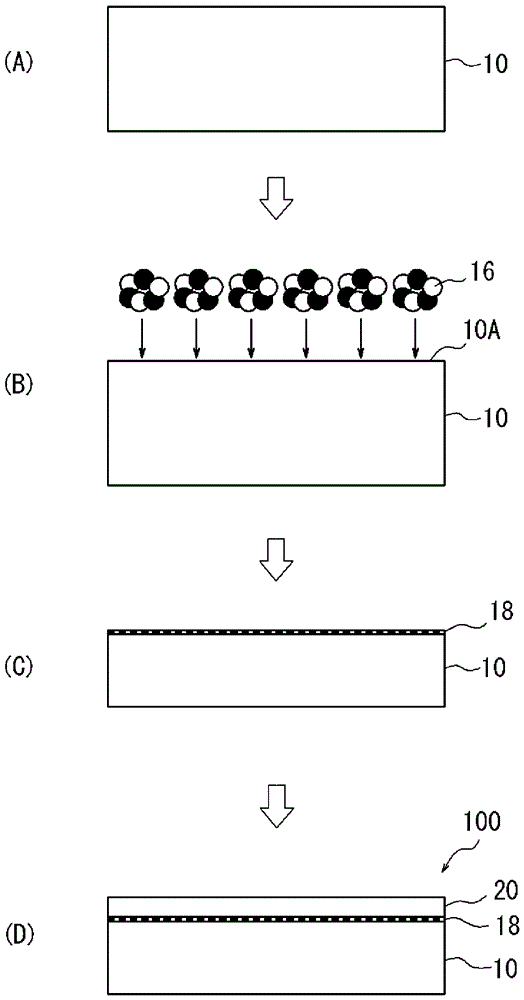

[0071] First, as a substrate of an epitaxial wafer, a silicon wafer having a diameter of 300 mm, a thickness of 775 μm, and a resistivity of about 0.003 Ω·cm was prepared. Next, using a cluster ion generator (manufactured by Nisshin Ion Machinery Co., Ltd., model: CLARIS), generate C 3 h 5 The clusters were irradiated on the surface of the silicon wafer as cluster ions under the condition that the acceleration voltage per carbon atom was 23.4 keV / atom. Here, the dose of cluster ions is 1.0×10 15 atom / cm 2 (Invention Example 1), 5×10 15 atom / cm 2 (Invention Example 2), 2×10 14 atom / cm 2 (invention example 3) these three levels. Next, the silicon wafer was transported to a monolithic epitaxial growth apparatus (manufactured by Applied Materials, Inc.), and hydrogen baking was performed at a temperature of 1120° C. for 30 seconds in the apparatus. The...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More