Method of Eliminating DC Offset in Cot Ripple Compensation Circuit

A technology of ripple compensation and DC offset, applied to electrical components, output power conversion devices, etc., can solve problems such as large output DC offset, and achieve the effect of output offset elimination

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further elaborated below in conjunction with the accompanying drawings and specific embodiments.

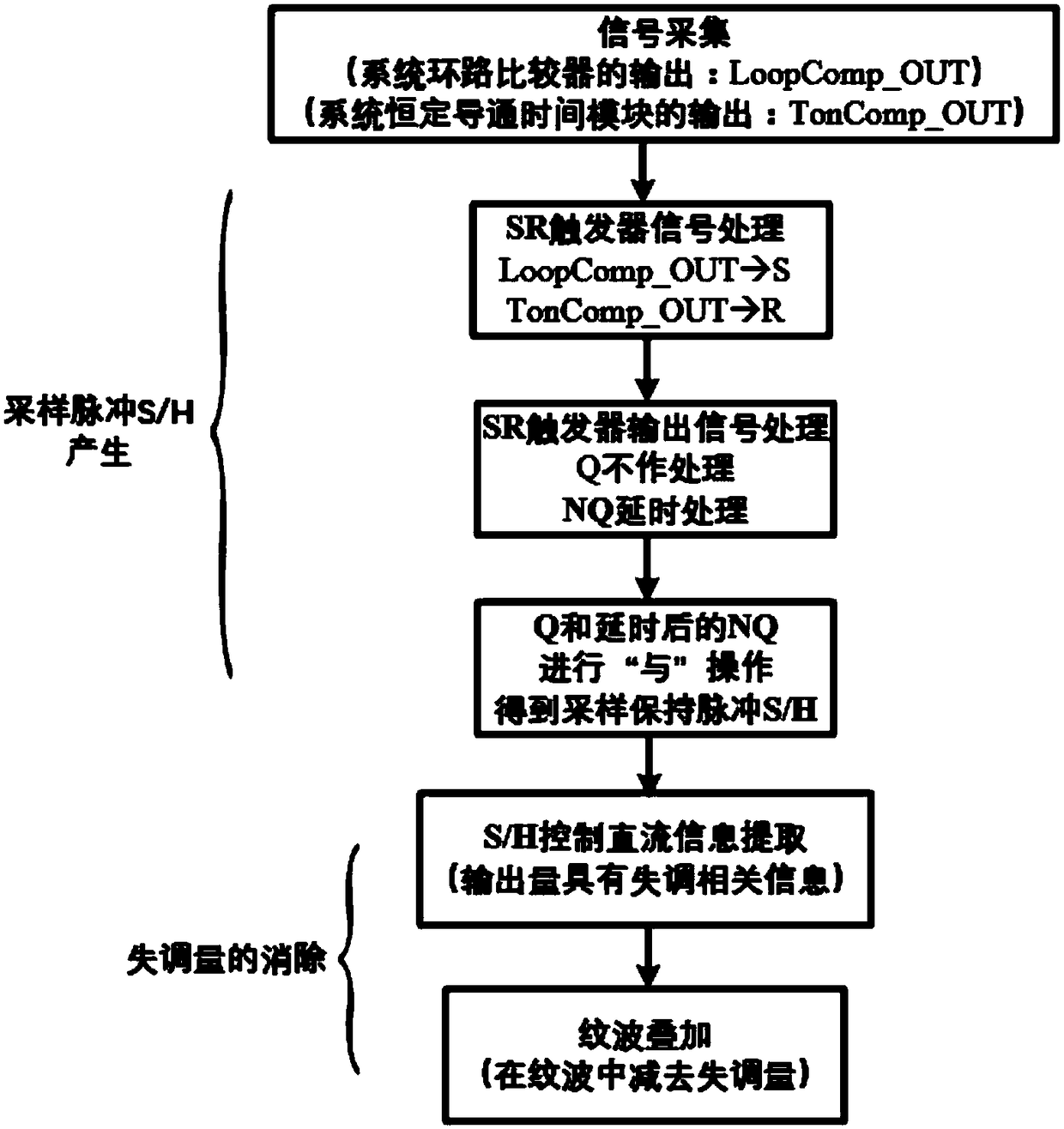

[0034] Such as figure 2 It is a flow chart of the DC offset elimination method in the COT ripple compensation circuit proposed by the present invention, including the sampling pulse S / H generation process and the offset elimination process.

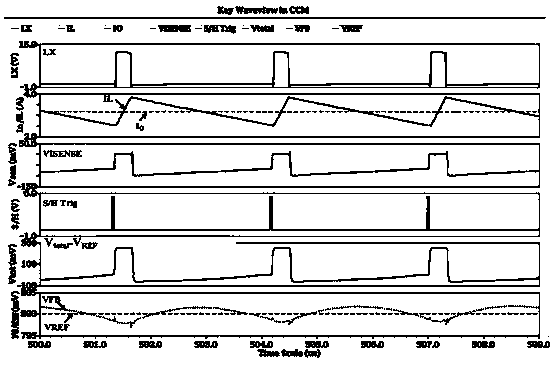

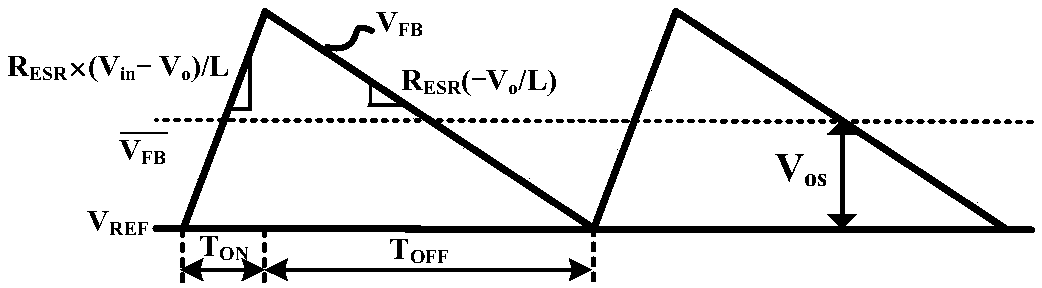

[0035] The implementation of the DC offset elimination method in the COT ripple compensation circuit proposed by the present invention is shown in the figure image 3 As shown in the block diagram, the inductor current ripple information after half-period sampling is amplified by K times full differential through the pre-amplifier, and then sent to the DC flow extraction circuit for DC flow extraction. The core of the present invention lies in the generation of DC flow extraction pulses and the coordination The ripple summing circuit subtracts the extracted amount.

[0036] The ripple DC flow extractio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More