A two-step incremental analog-to-digital converter and two-step conversion method

A technology of digital converters and analog converters, applied in the direction of analog-to-digital converters, etc., to achieve the effects of low power consumption, increased size, and small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

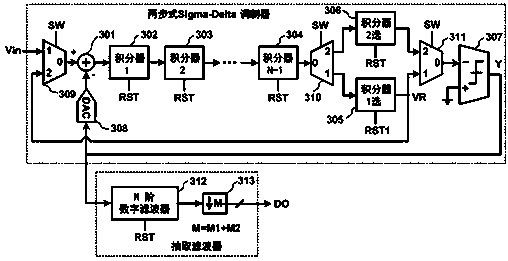

[0051] Such as image 3 , the two-step incremental analog-to-digital converter (N order-N order) provided by the present invention includes an adding circuit 301, N-1 cascaded integrators 302-304, first and second sub-steps Select the two-step delta-sigma modulator (Sigma-Delta modulator), and a decimation filter composed of an N-order digital filter 312 and a decimator 313, wherein: an input terminal of the first multiplexer 309 is connected to the input signal Vin, an output terminal 0 is connected to the addition circuit 301, and the addition circuit The output terminal of 301 is connected to N-1 cascaded integrators 302-304, and the output terminal of N-1 cascaded integrators 302-304 is connected to the 0 end of the second multiplexer 310, and the second multiplexer 310 The output terminal 1 of the output end is connected with the first step-by-step selection integrator 305, and the 2-end is connected with the second step-by-step selection integrator 306, and the output t...

Embodiment 2

[0067] Such as Figure 5 , the two-step incremental analog-to-digital converter (2nd-2nd order) provided by the present invention includes an addition circuit 501, an integrator 502 (N at this time is equal to 2), the first and second step-by-step selection integration A two-step delta-sigma modulator (Sigma-Delta modulator) composed of 503, 504, comparator 505, first, second, and third multiplexers 506, 507, 508, and a 2-order digital filter 509 and the decimation filter formed by the decimator 510, since the comparator is single-bit quantization, its output level number L=2, so no special DAC circuit is needed, wherein: 1 end of the first multiplexer 506 is an input terminal connection The input signal Vin, the output terminal 0 are connected to the addition circuit 501, the output terminal of the addition circuit 501 is connected to the input terminal of the integrator 502, the output terminal of the integrator 502 is connected to the 0 end of the second multiplexer 507, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More