Array substrate, preparation method of array substrate and display device

A technology for array substrates and substrates, applied in semiconductor/solid-state device manufacturing, instruments, semiconductor devices, etc., can solve the problems of small grain size, low crystal quality, and limited electrical performance of thin-film transistor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

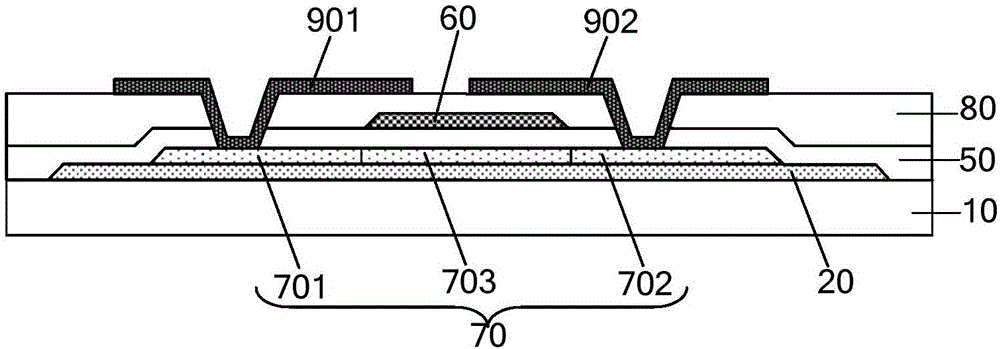

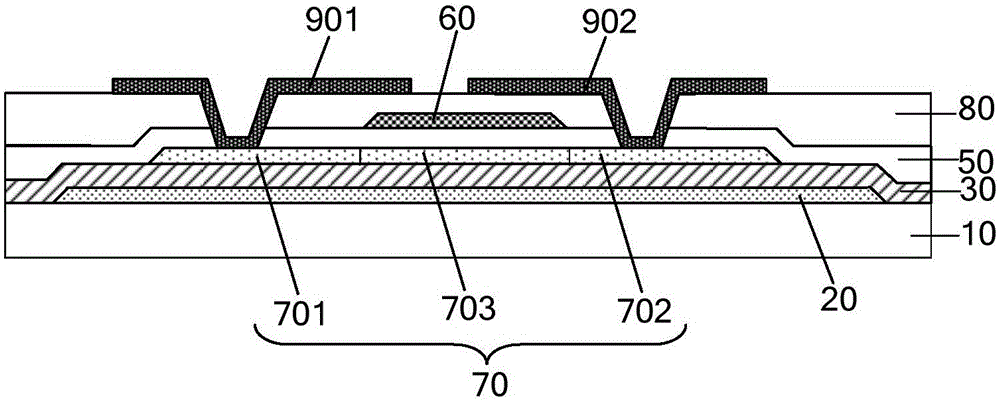

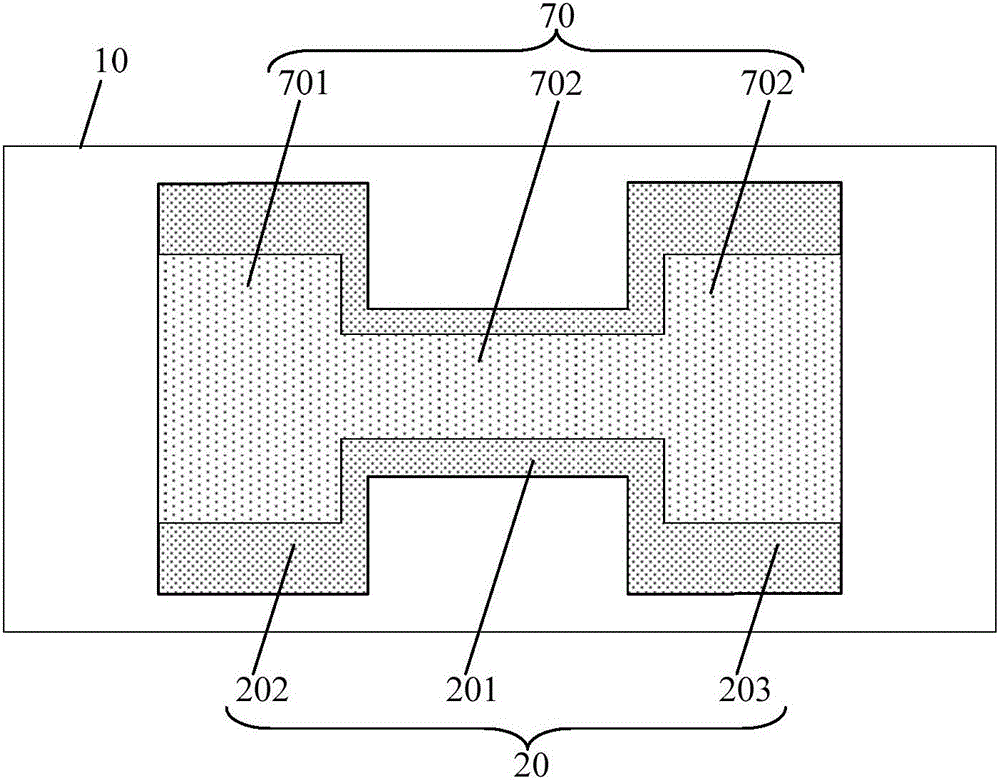

[0083] The embodiment of the present invention also provides a method for preparing an array substrate, such as figure 1 and figure 2 As shown, a polysilicon thin film transistor is formed on a substrate 10, and the polysilicon thin film transistor includes an active layer 70, and the active layer 70 includes a source region 701, a drain region 702, and a The channel region 703 between; wherein, the active layer 70 is obtained by performing ion implantation to the polysilicon layer; the polysilicon layer 402 is obtained by performing excimer laser annealing on the amorphous silicon layer; the method also includes: forming the polysilicon layer Before the thin film transistor, a metal light-shielding layer 20 corresponding to the active layer 70 is formed on the substrate 10; the orthographic projection of the metal light-shielding layer 20 on the substrate 10 completely covers the orthographic projection of the channel region 703 on the substrate 10, and The metal light-shie...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thermal conductivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More