Semiconductor structure and forming method thereof

A semiconductor, regular polygon technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as cracking or falling off, chip packaging failure, affecting product yield, etc. The effect of shedding and uniform stress distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Specific implementations of the semiconductor structure and its forming method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

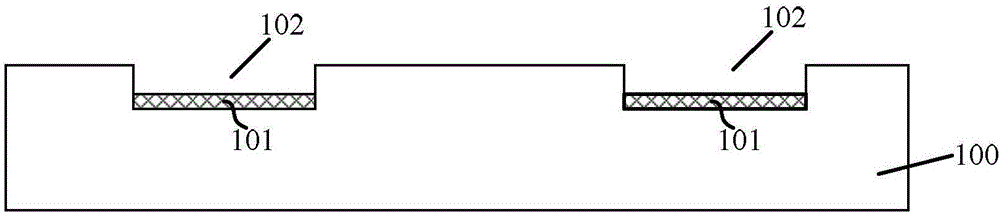

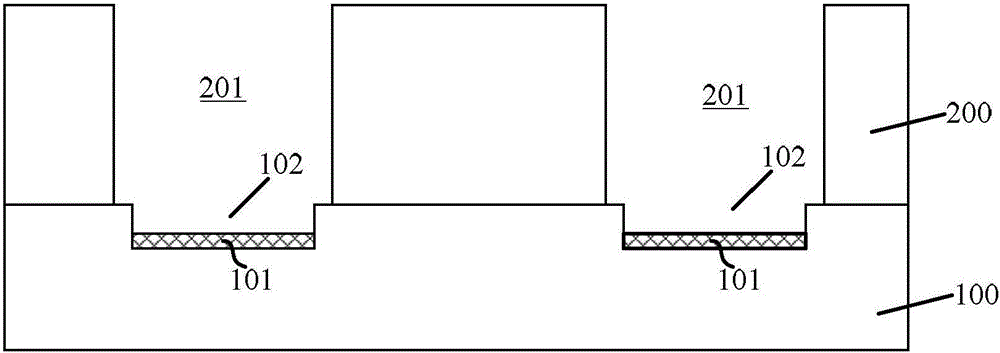

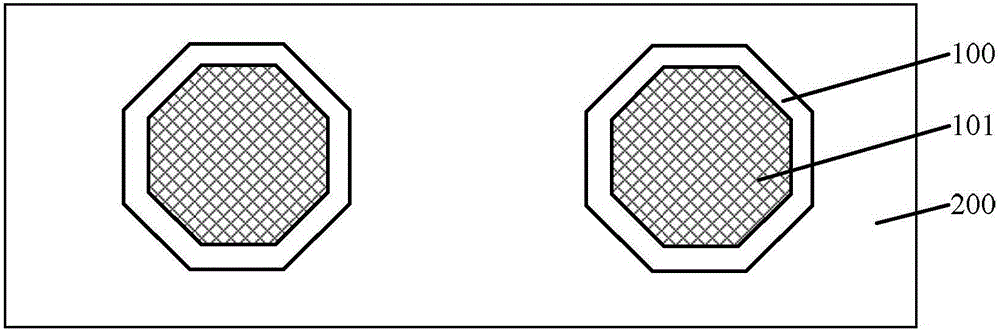

[0022] Please refer to figure 1 , providing a substrate 100, the surface of the substrate 100 has a groove 101, and the groove 102 exposes the surface of the metal layer 101.

[0023] The substrate 100 is a multi-layer structure, including a semiconductor layer and a dielectric layer located on the surface of the semiconductor layer, a semiconductor device located in the semiconductor layer, a metal interconnection structure in the dielectric layer, and the like. The metal layer 101 is a solder pad, which serves as a connection structure with an external circuit after packaging, and the material of the metal layer 101 can be metal such as Al, Cu or Au. The size of the metal layer 101 may be the same as the size of the groove 102 or larger than the size of the groove 102 .

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More