A vertical nanowire device with sheath channel structure and its preparation method

A channel structure and nanowire technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing device power consumption, difficult control of channel cross-sectional morphology, and device performance degradation, etc. Small leakage current and improved short channel effect control ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0084] Below in conjunction with accompanying drawing, further describe the present invention through embodiment, but do not limit the scope of the present invention in any way.

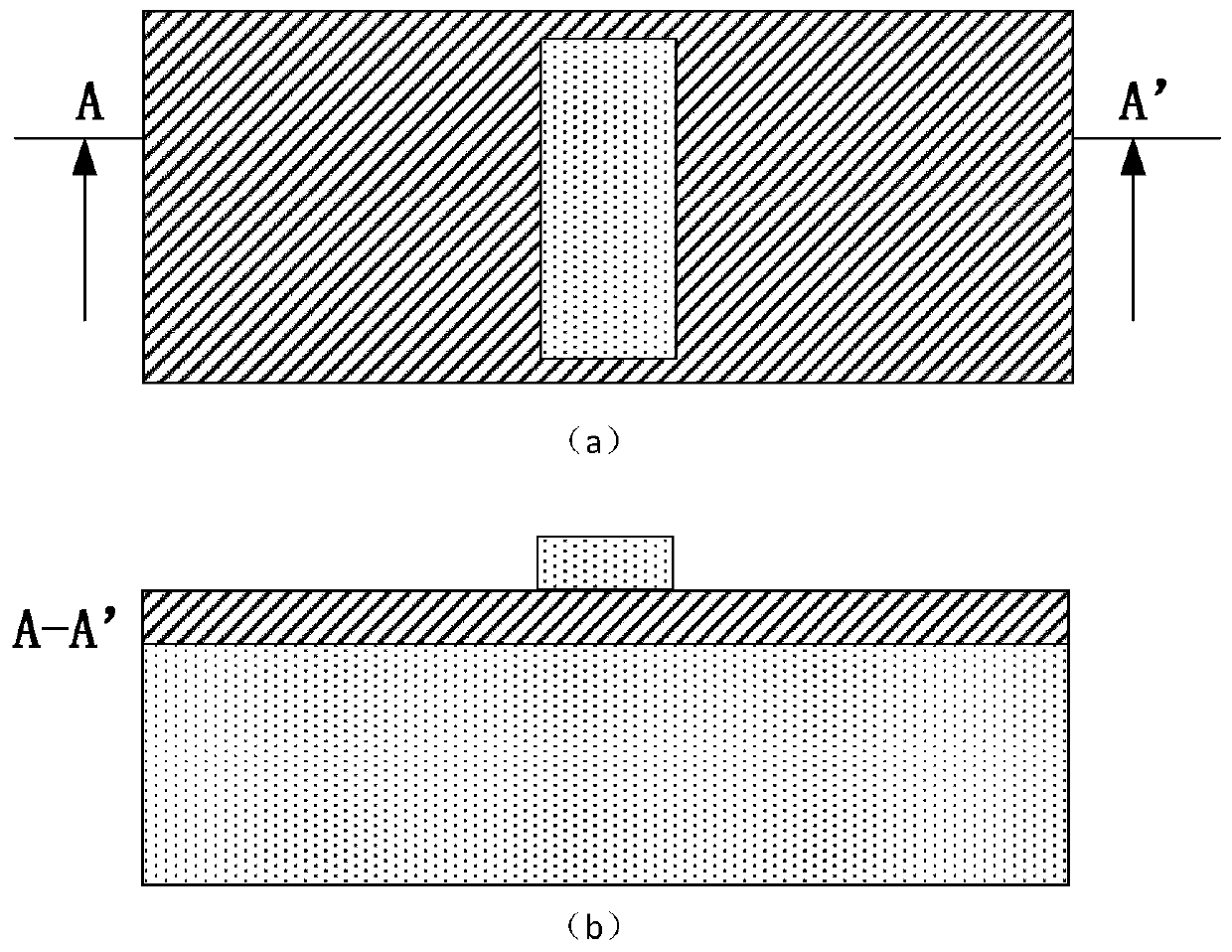

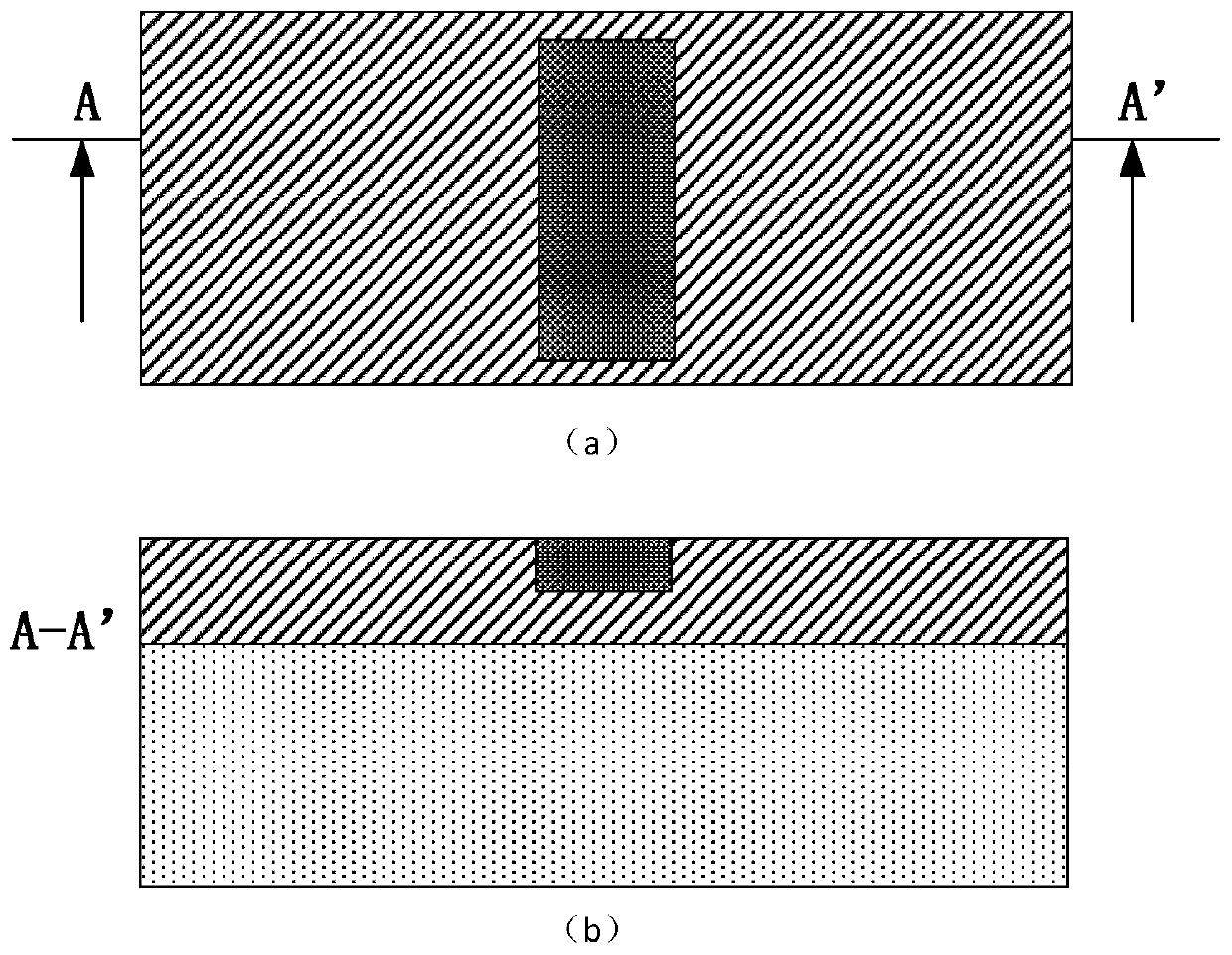

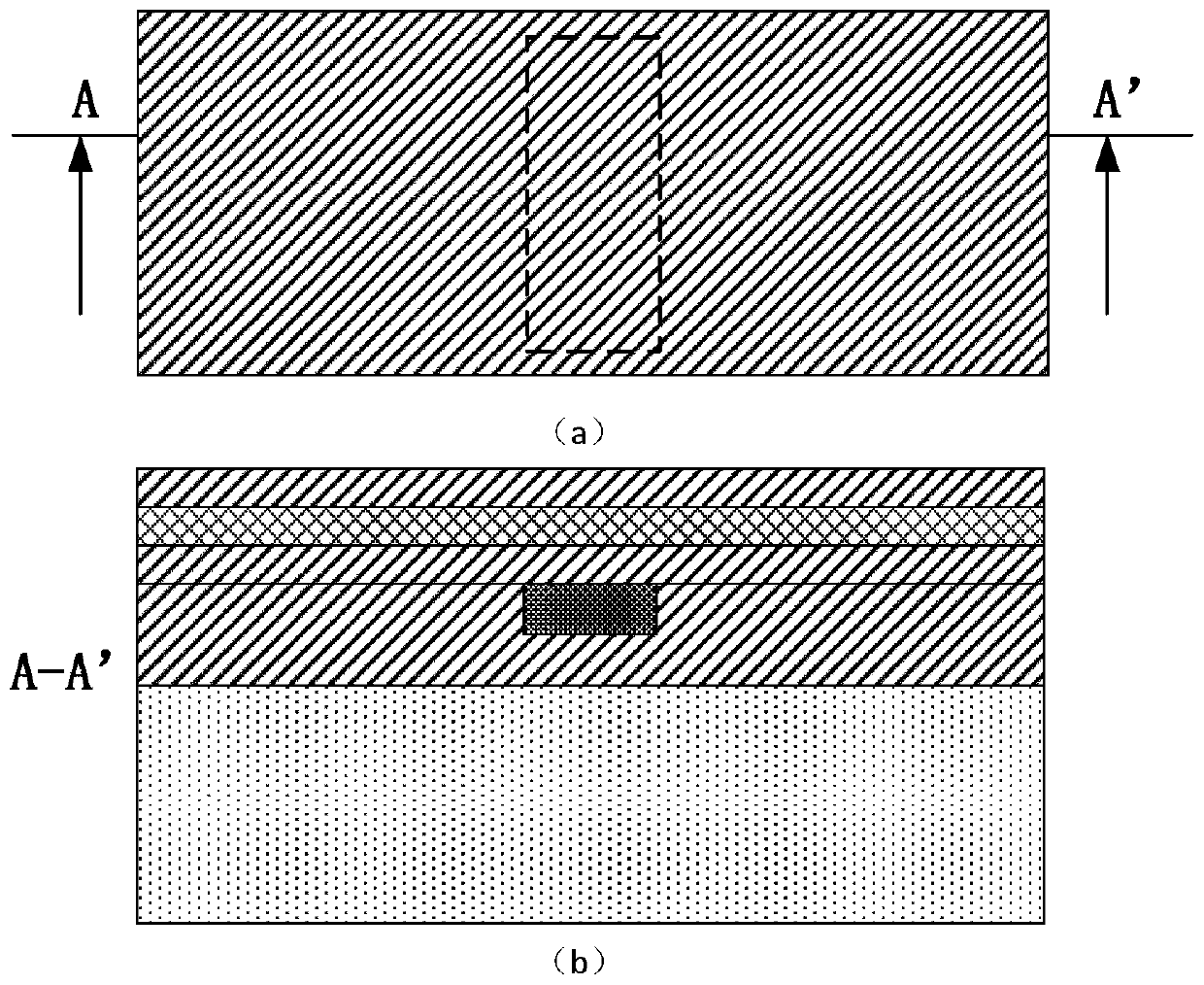

[0085] The invention provides a vertical nanowire device with a sheath channel structure and a preparation method thereof, which combines etching through holes, depositing channel materials, and filling silicon dioxide to obtain an integrated vertical nanowire device with a sheath channel structure; Including providing a semiconductor substrate to realize device isolation; forming a heavily doped "lower active region"; depositing dummy gate stacks; forming vertical sheaths by etching vias, depositing channel materials, and filling silicon dioxide Layer channel structure; form the heavily doped "upper active region" of the device by deposition and etching; remove the dummy gate, deposit HK, MG and form the gate electrode; form metal contacts at each end of the device; follow-up according to the existin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More