Clock generation circuit for analog-to-digital converter

A clock generation circuit, analog-to-digital converter technology, applied in the direction of generating electrical pulses, pulse generation, electrical components, etc., can solve problems such as wrong trigger sampling time, deterioration of ADC signal-to-noise ratio, and wrong sampling of analog input signal amplitude, to achieve Improve ADC signal-to-noise ratio, reduce harsh requirements, and improve the effect of clock signal quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described in detail below in combination with specific embodiments.

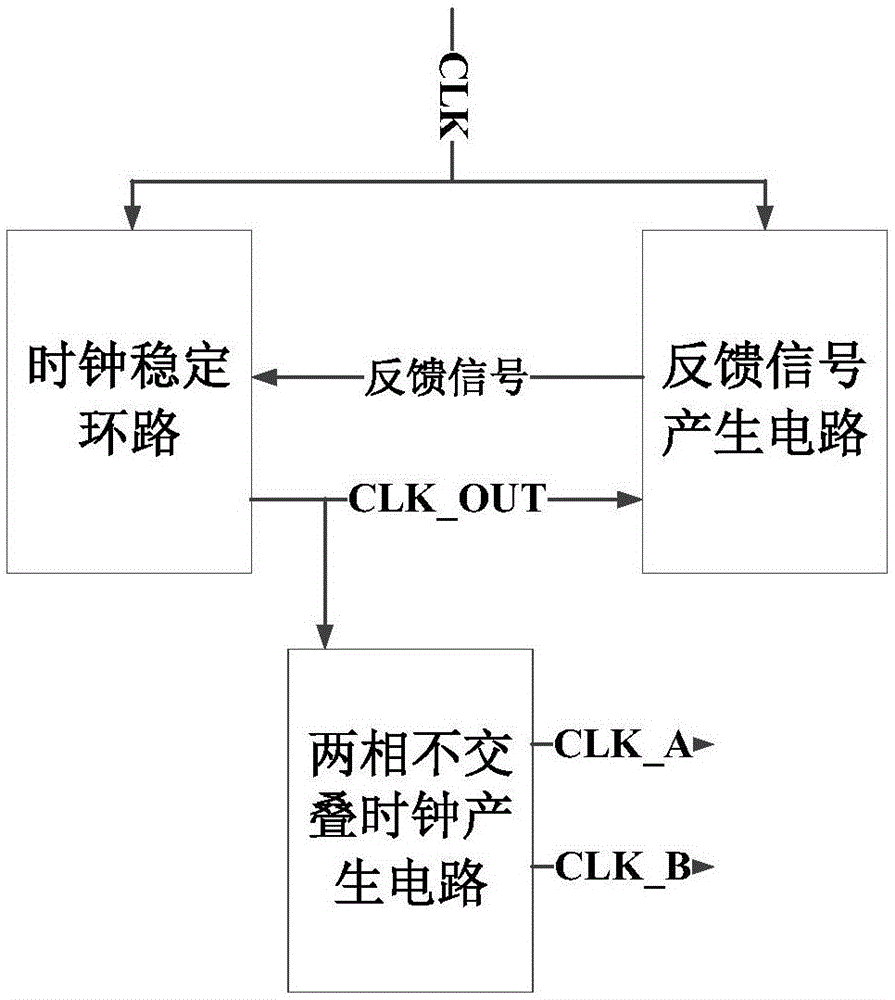

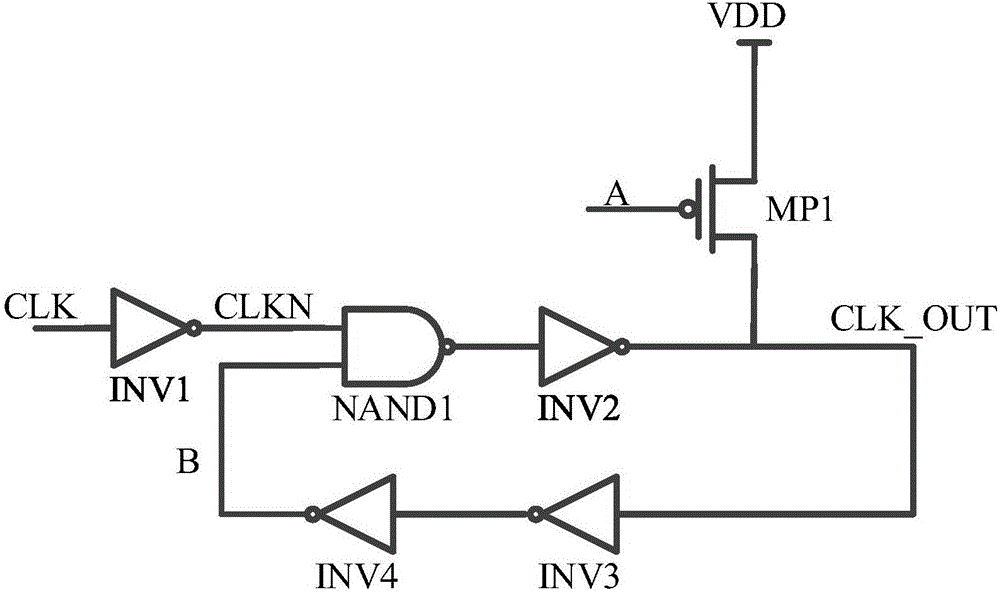

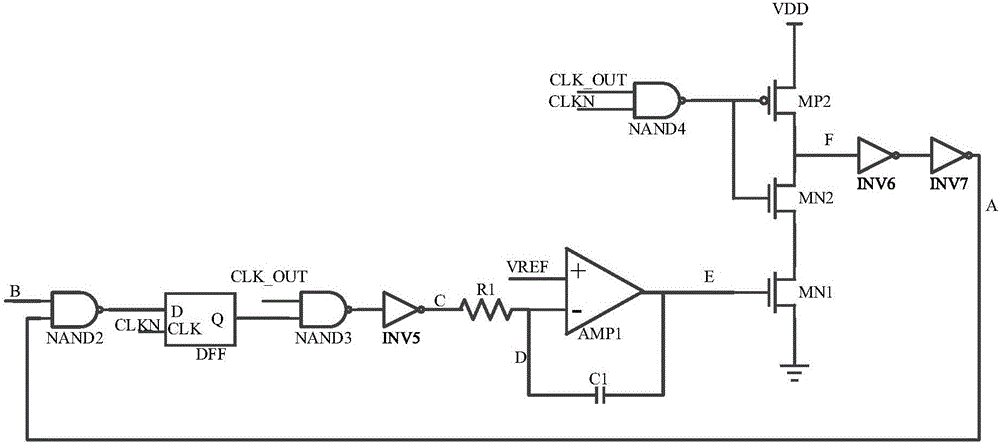

[0020] Such as figure 1 As shown, the design idea of the present invention is to generate a stable clock signal through the clock stabilization loop, and the used clock stabilization loop itself reduces the duty ratio of the output clock signal CLK_OUT through the NAND gate NAND1, and increases the duty ratio of the output clock signal CLK_OUT by pulling up the PMOS transistor MP1. Output clock signal CLK_OUT duty cycle. Through the feedback signal generation circuit part, the feedback signal A is generated according to the input clock CLK and the output clock CLK_OUT, so as to realize the adjustment of the duty ratio of the output clock and the elimination of clock jitter.

[0021] Such as figure 1 As shown, the present invention proposes a clock generation circuit for an analog-to-digital converter, including a clock stabilization circuit and a two-phase non...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More