A chip thermal layout method

A chip and layout technology, applied in the direction of instrumentation, calculation, electrical digital data processing, etc., can solve problems such as long time, long optimization process, and irregular coding, so as to reduce hot spot temperature, improve performance and reliability, and reduce temperature difference Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings.

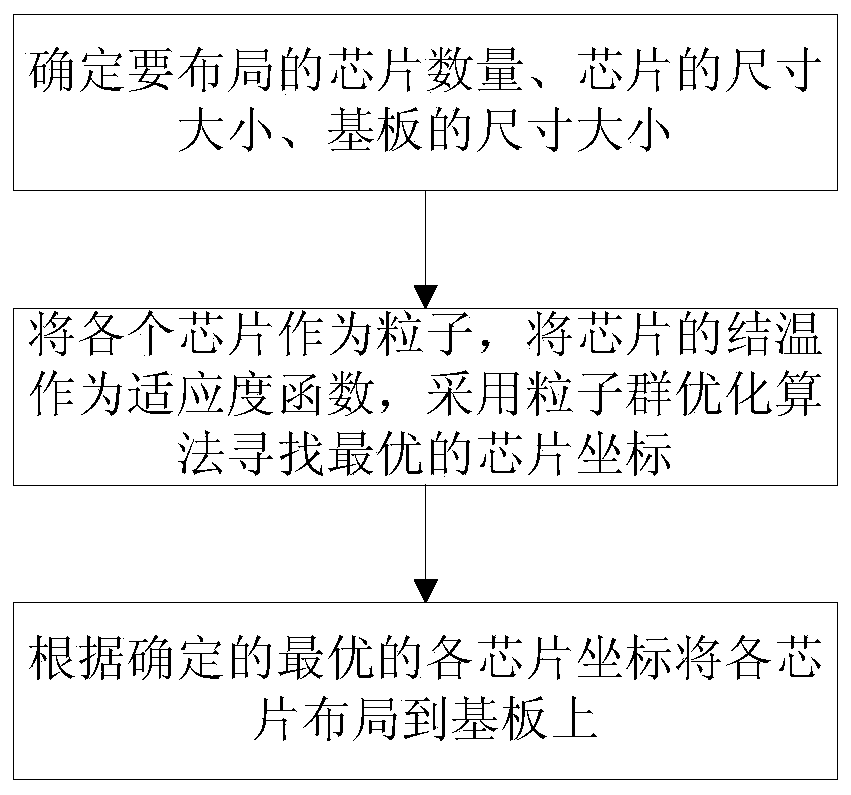

[0055] A chip thermal layout method based on the combination of particle swarm optimization and junction temperature, such as figure 1 shown, including:

[0056] Step 1. Determine the number of chips to be laid out, the size of the chips, and the size of the substrate;

[0057] Step 2. Use each chip as a particle, and all chips on the substrate form a particle swarm, use the junction temperature of the chip as a fitness function, and use the particle swarm optimization algorithm to find the optimal chip coordinates;

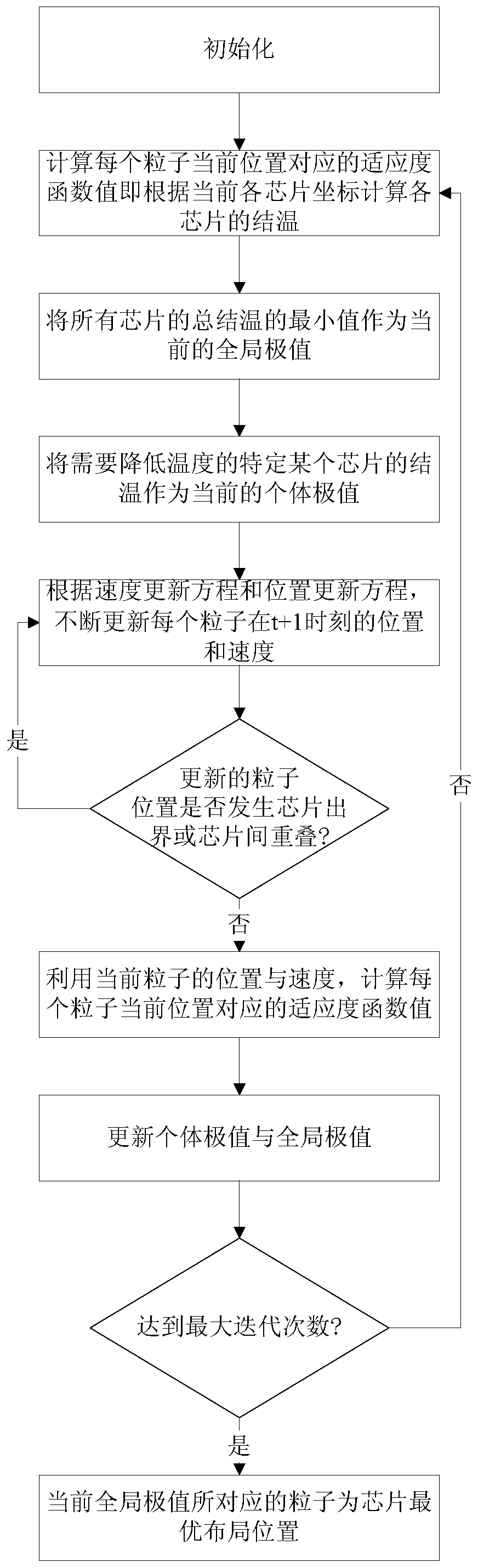

[0058] The particle swarm optimization algorithm is simpler than the rules of the genetic algorithm. It does not have the crossover, mutation and reversal operations of the genetic algorithm, but determines the search direction and step size according to its own speed, and has memory capabilities. The model is sim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More