Patents

Literature

112results about How to "Reduce hot spot temperature" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Catalyst for selectively oxidizing methyl acrylic aldehyde to synthesize methyl propenoic acid and its use

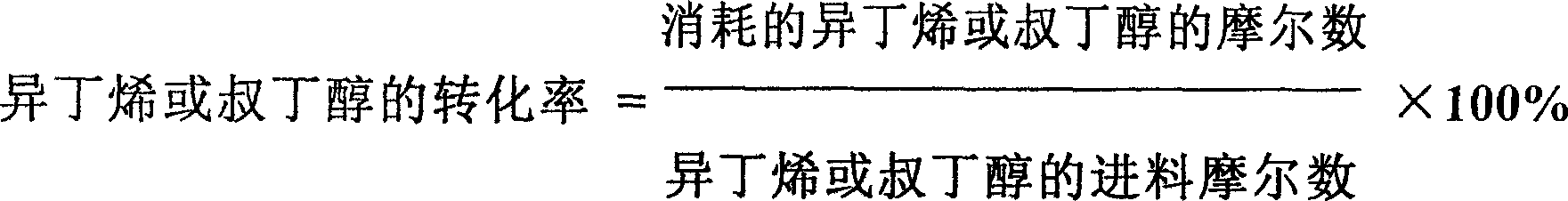

ActiveCN1647854AHigh reactivityHigh selectivityPhysical/chemical process catalystsOrganic compound preparationHeteropoly acidGas phase

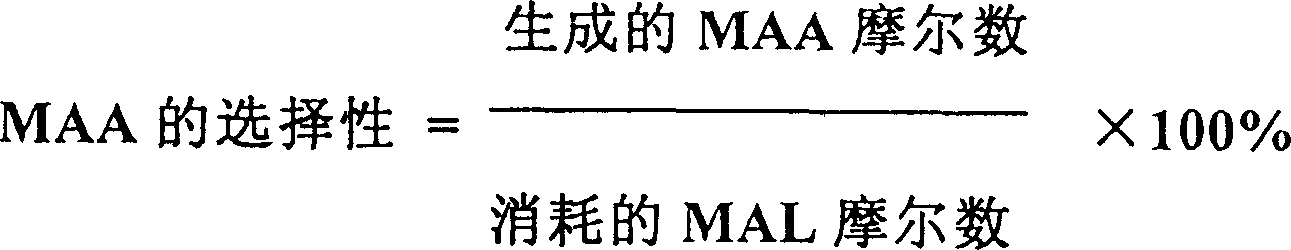

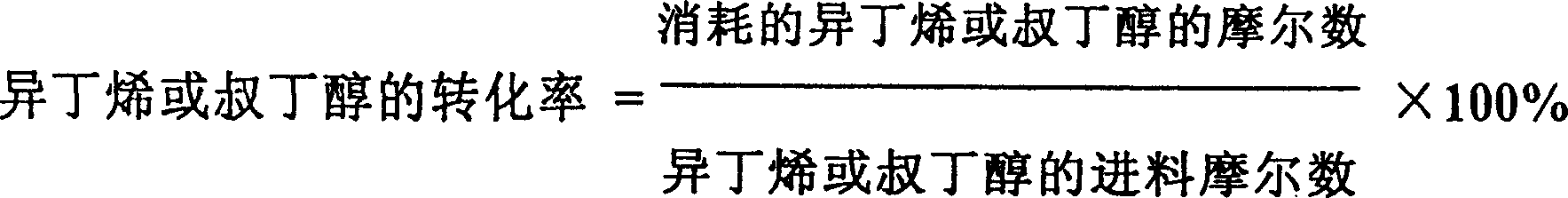

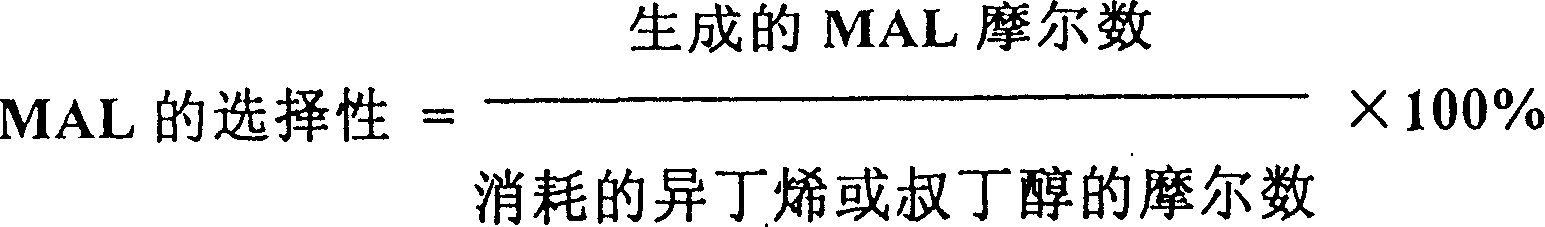

The present invention provides catalyst for selectively oxidizing methyl acrolein to synthesize methylpropenoic acid and its usage in catalyzing gas phase oxidation of methyl acrolein to synthesize methylpropenoic acid. The catalyst is one heteropoly acid salt containing Mo, P, K, Sb, Cu, As, etc., and has high catalytic activity and stability, long service life, methyl acrolein converting rate higher than 85 % and methylpropenoic acid selectivity over 87 % in the presence of molecular oxygen and diluting gas.

Owner:SHANGHAI HUAYI NEW MATERIAL

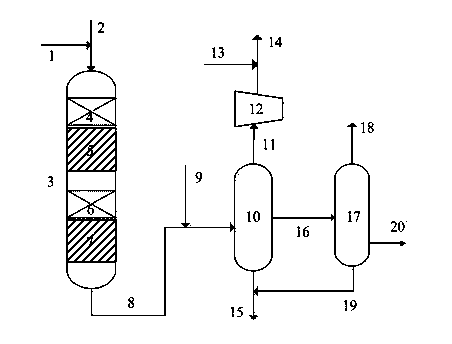

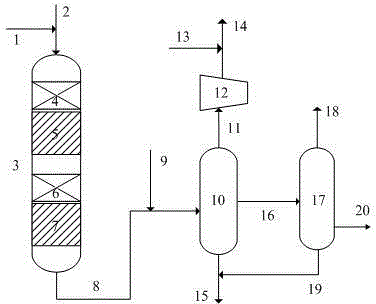

Catalyst for selectively oxidizing tertiary butanol or isobutene to synthesize methyl acrylic aldehyde and its use

ActiveCN1647853AHigh activityImprove thermal conductivityPhysical/chemical process catalystsOrganic compound preparationGas phaseCatalytic oxidation

The present invention provides a kind of catalyst for selectively oxidizing tertiary butanol or isobutene to synthesize methyl acrolein and its preparation process and application in gas phase catalytic oxidizing synthesis of methyl acrolein. The catalyst of the present invention is one kind of composite oxide containing Mo, Bi, Fe, Co, Sb, Pb, Yb, etc. and has high catalytic activity and stability, long service life, isobutene converting rate higher than 95 % and methyl acrolein selectivity over 86 % in the presence of molecular oxygen.

Owner:SHANGHAI HUAYI NEW MATERIAL

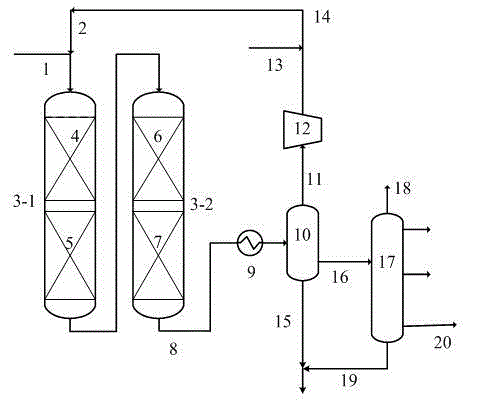

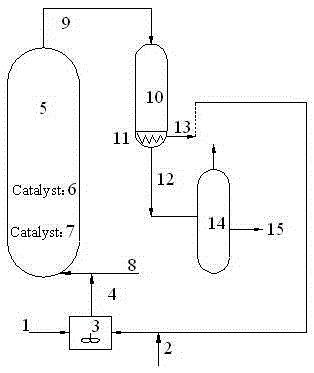

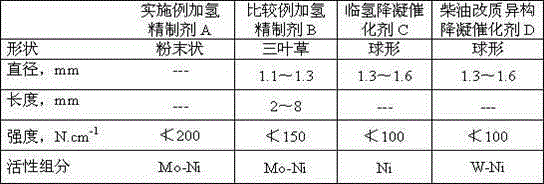

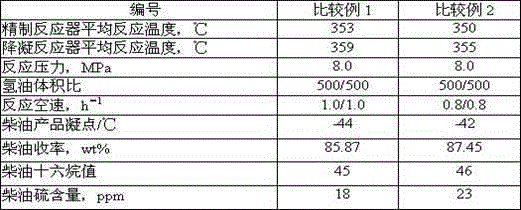

Method for producing diesel oil with low condensation point by catalyst gradation technology

ActiveCN103805257ALow yieldGuaranteed yieldTreatment with hydrotreatment processesHydrogenation reactionSulfur

The invention discloses a method for producing diesel oil with a low condensation point by catalyst gradation technology. The method comprises the following steps: mixing a diesel oil raw material with hydrogen, orderly passing through at least two hydrogenation reaction zones connected in series, wherein in the material flowing direction, each hydrogenation reaction zone orderly comprises a hydro-refining dewaxing catalyst composite bed layer filled with a mixture of a hydro-refining catalyst and a hydro-upgrading isodewaxing catalyst, and a hydrodewaxing catalyst bed layer; performing separation and fractionation of the reaction effluent from the last hydrogenation reaction zone to obtain the diesel oil product with a low condensation point. The method of the invention reasonably combines and utilizes the temperature increase of the hydro-refining and hydro-upgrading dewaxing process with the temperature decrease of the hydrodewaxing process, improves the diesel oil yield and the cetane value while producing diesel oil with a low condensation point and low sulfur, reduces the hot-spot temperature of the device, prolongs the running period, also reduces the cold hydrogen consumption or the combustion gas loss of a heating furnace, and saves operation cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

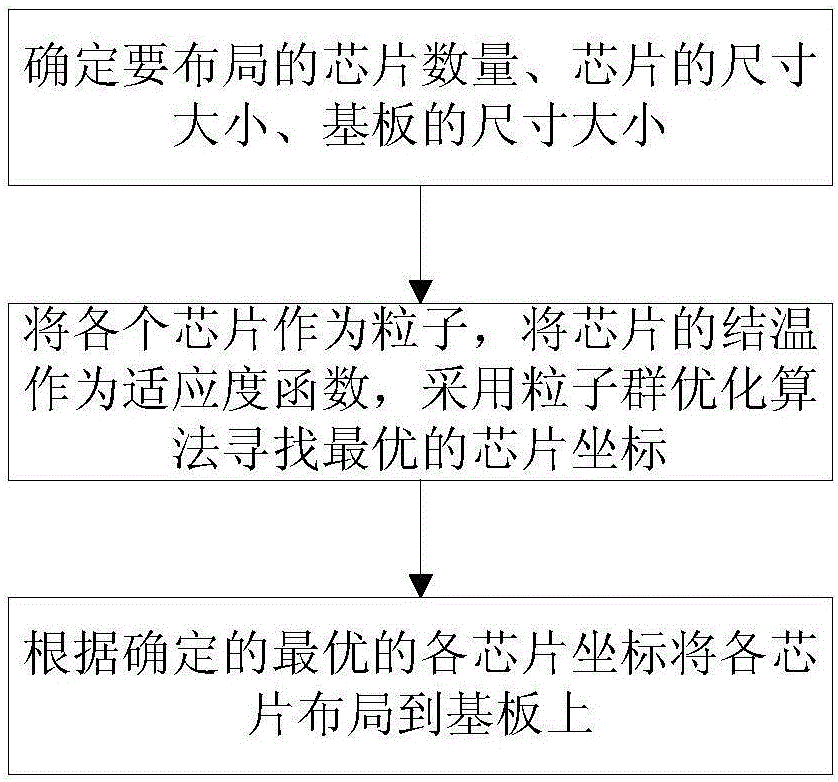

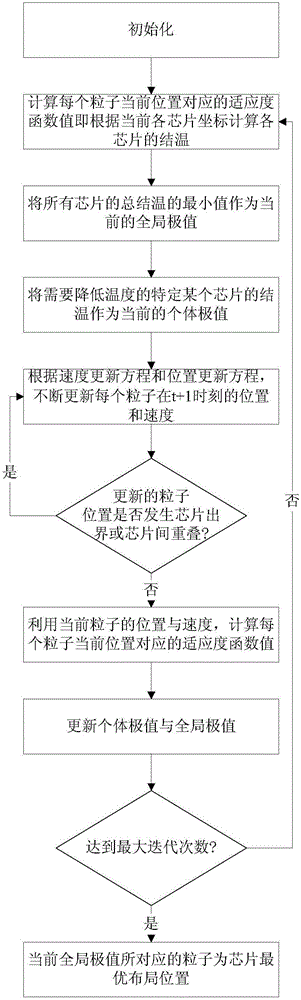

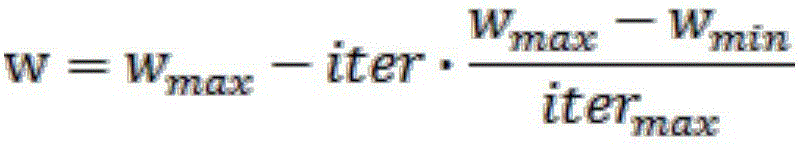

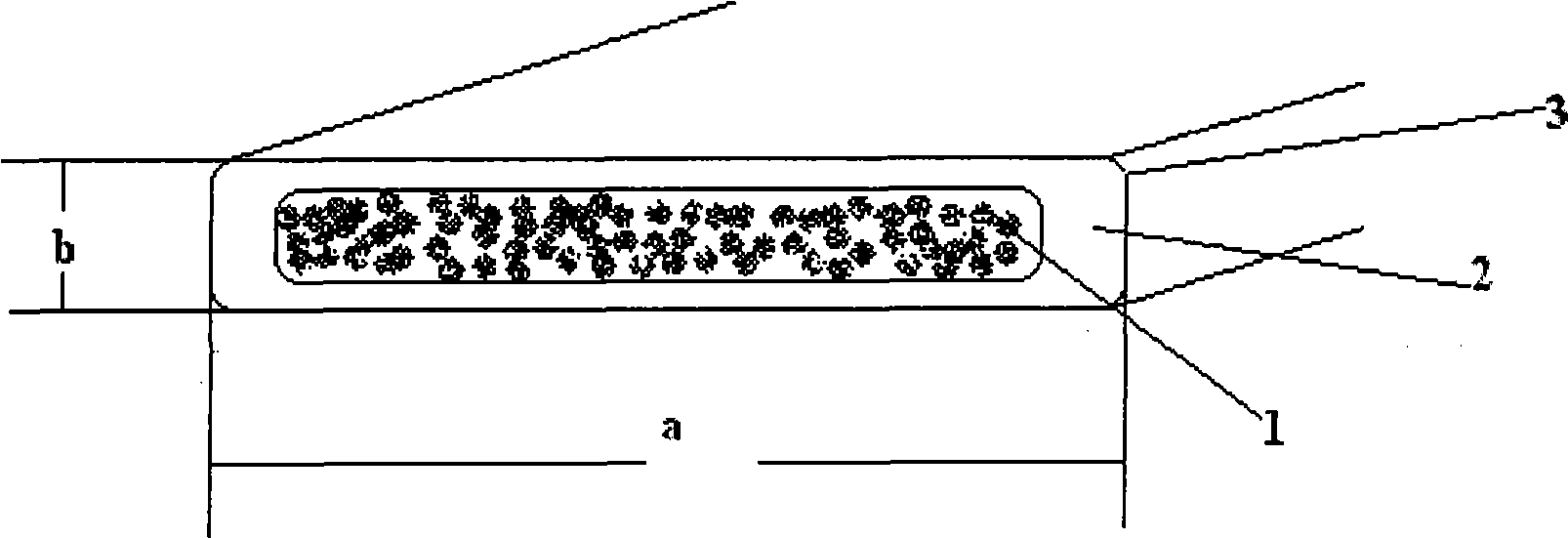

Chip hot layout method

ActiveCN106599428AMeet design requirements for thermal layoutReduce hot spot temperatureComputer aided designSpecial data processing applicationsBaseboardJunction temperature

The present invention provides a particle swarm optimization and junction temperature combination-based chip hot layout method. The method comprises the steps of determining a number and sizes of chips to be distributed, and a size of a baseboard; using each chip as a particle, wherein all chips on the baseboard form a particle swarm, using a junction temperature of the chip as a fitness function, and seeking optimal chip coordinates by using a particle swarm optimization algorithm; and distributing each chip on the baseboard according to the determined optimal coordinates of each chip. In the method, the junction temperature of any chip can be designated as the fitness function by taking the advantage of the particle swarm optimization algorithm, the actual size of the chip is taken into account so as to prevent the chip to be out of the bound and overlap, so that all chips on the baseboard are distributed reasonably, further, temperature of a certain high-power chip, a chip not resisting high temperature, or a chip with special requirements reaches a minimum level as much as possible, therefore, hot-spot temperature on the whole baseboard is further reduced, a temperature difference of chips is reduced, and the performance and reliability of the device are improved.

Owner:NORTHEASTERN UNIV

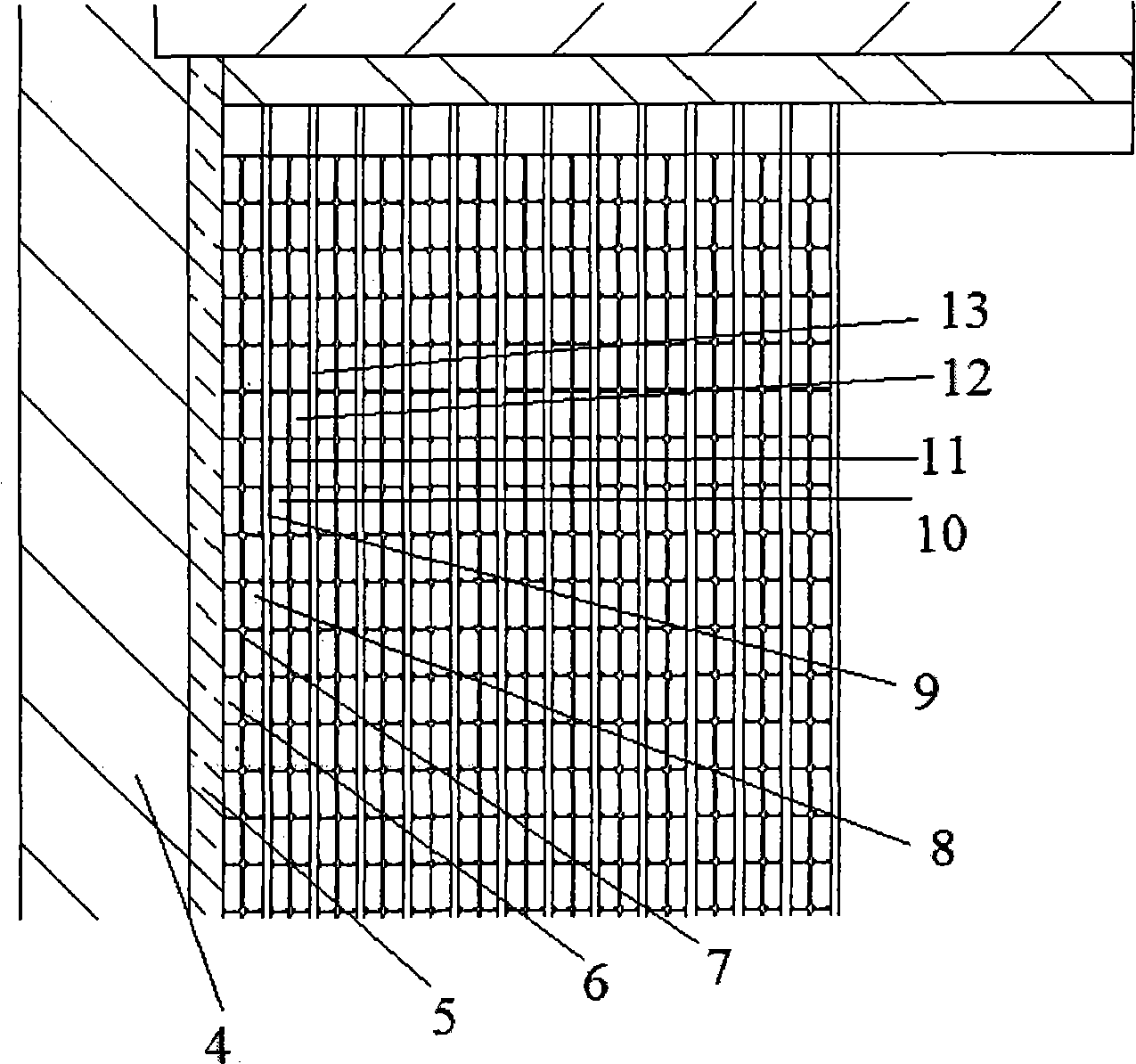

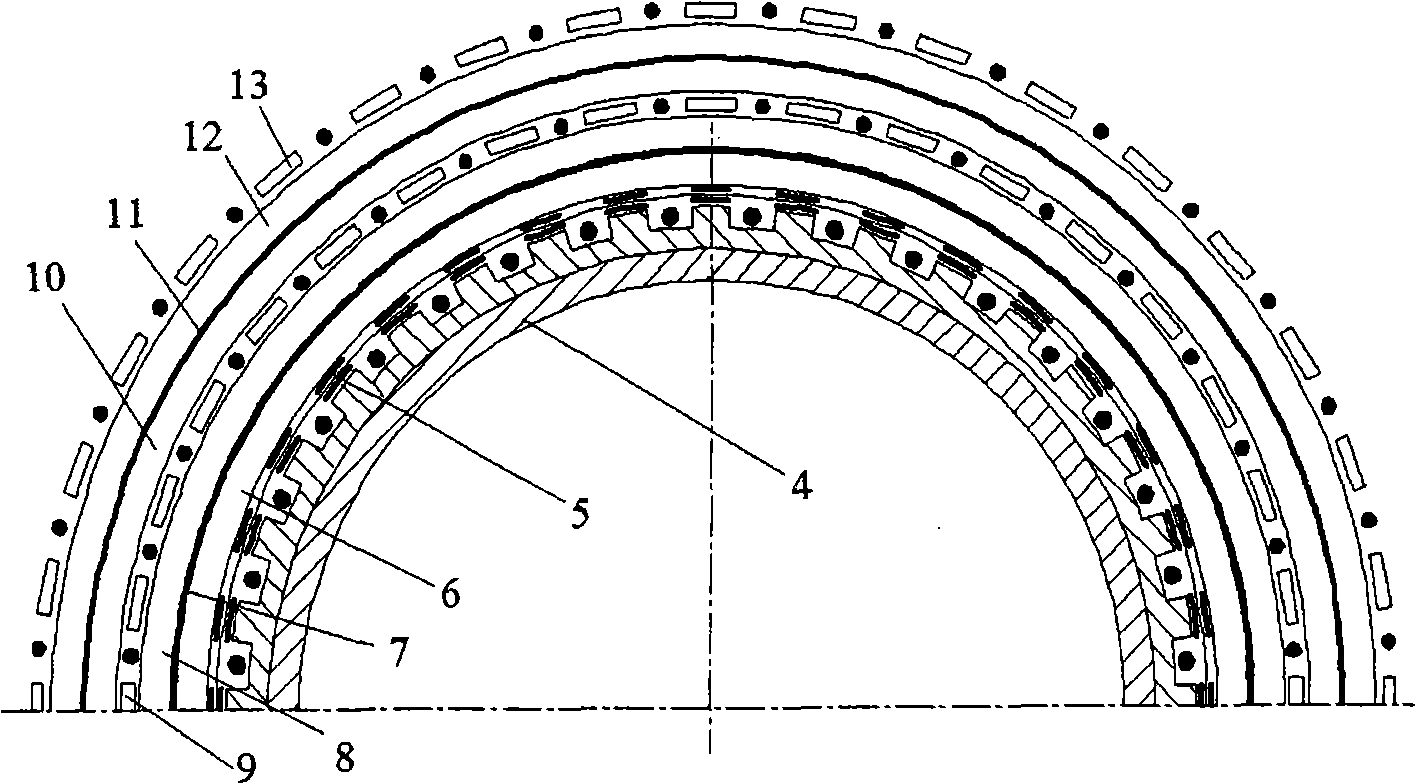

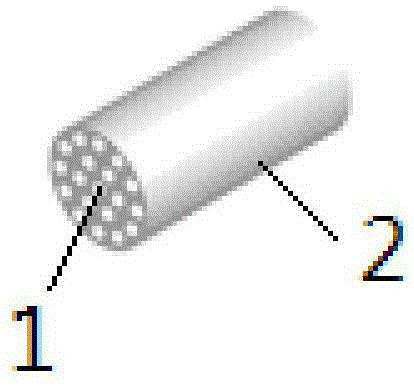

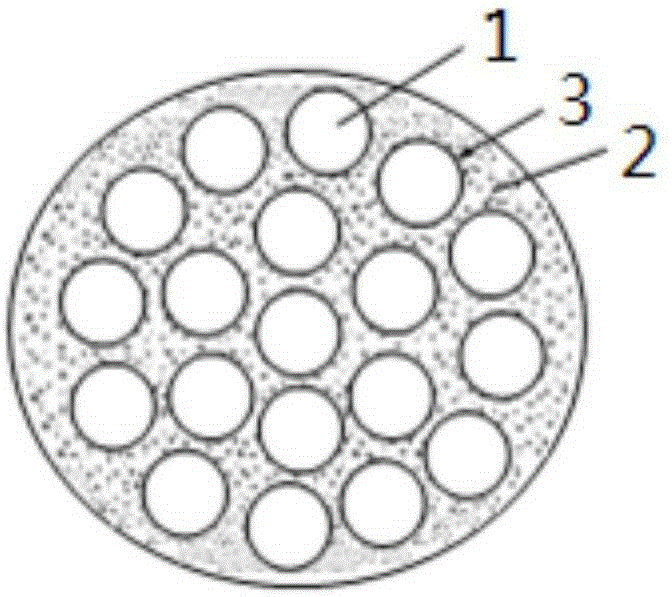

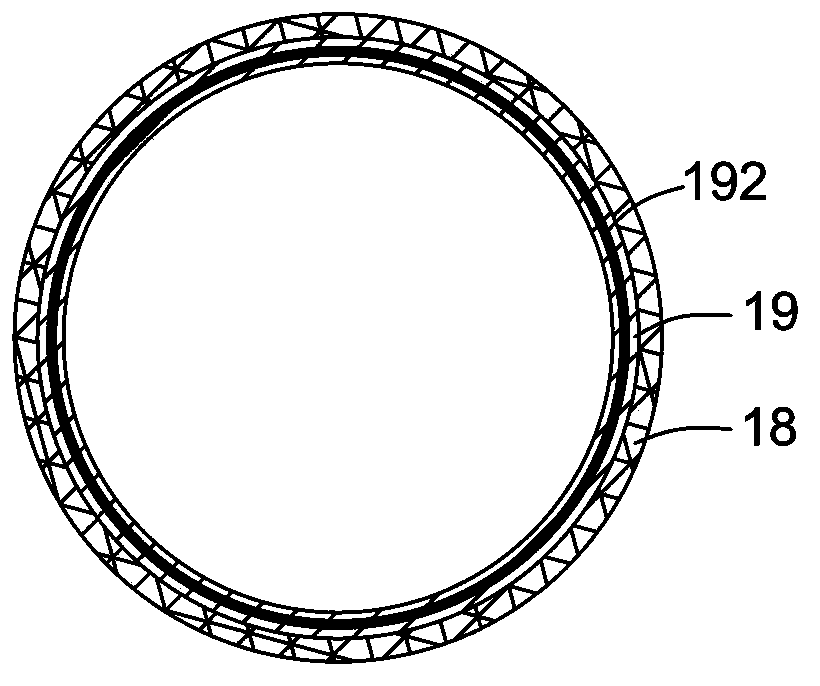

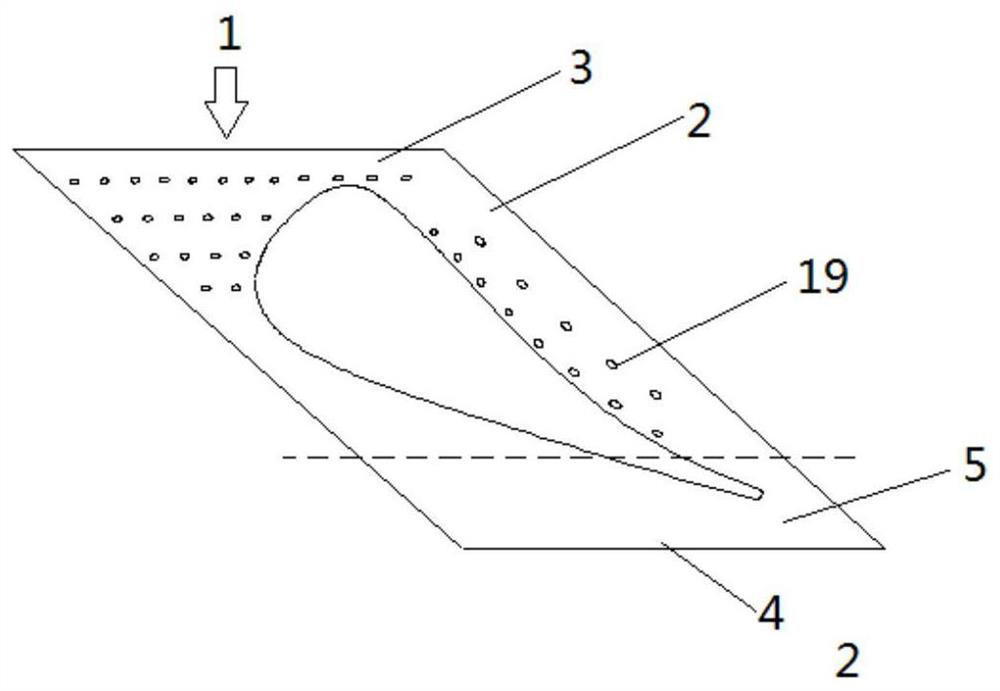

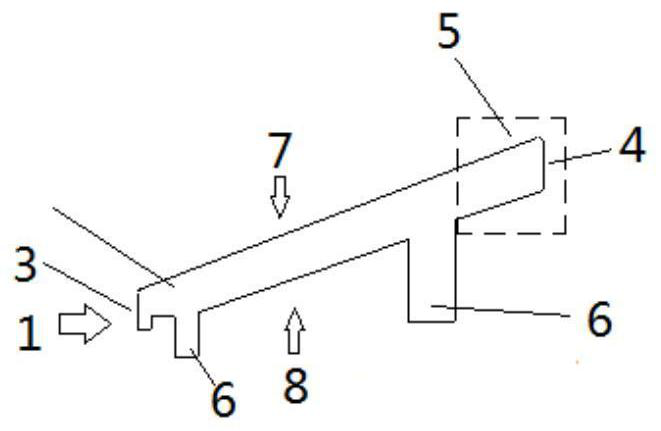

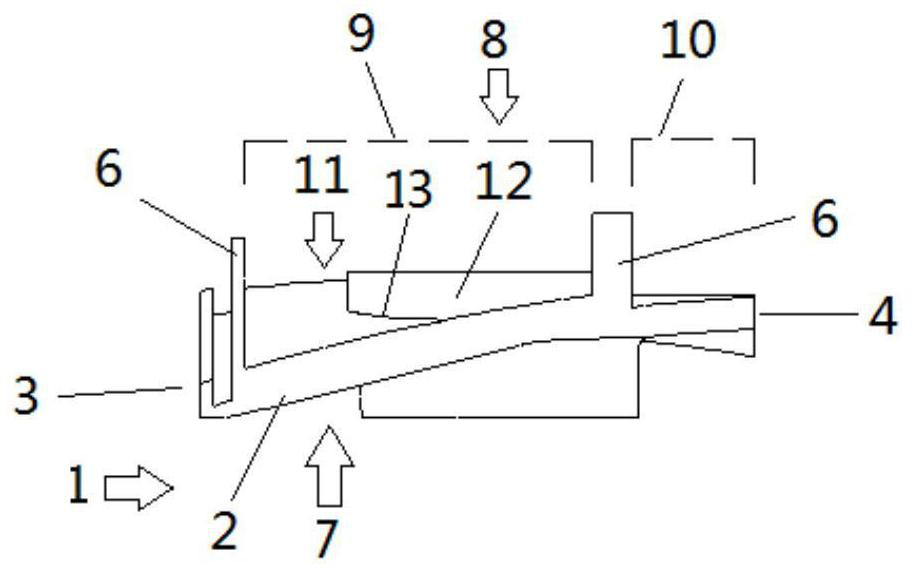

Coil used for fast impulse superconducting magnet winding structure

ActiveCN101499351AHigh mechanical rigidityImprove stabilitySuperconductors/hyperconductorsSuperconductor devicesEpoxyHigh energy

A coil used for fast pulse superconducting magnet winding structure has an epoxy gasket (5) arranged on a frame (4) with a hole; a first layer of superconducting winding (6) is winded on the epoxy gasket (5); a layer of epoxy glass ribbon (7) is winded between the first layer of the superconducting winding (6) and a second layer of superconducting winding (8) which are bonded together by low-temperature epoxy resin; and epoxy glass steel strips (9) are distributed on the surface of the second layer of the superconducting winding (8) at equal intervals along the circumference direction of the winding. The superconducting wire used by the superconducting winding of the coil is formed by coating a composite matrix (2) consisting of CuNi and copper outside a superconductor (1), wherein an insulating layer (3) is coated on the composite matrix (2). The coil has higher mechanical stability and better heat transfer characteristics, and is suitable for a fast-excitation large-scale superconducting coil with high energy-storing density and high magnetic field.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

Combined process method for producing clean diesel oil with low condensation point

ActiveCN103805258AGuaranteed yieldRealize comprehensive utilizationTreatment with hydrotreatment processesFractionationLiquid gas

The invention discloses a combined process method for producing clean diesel oil with a low condensation point. The method comprises the following steps: mixing a diesel oil raw material with hydrogen, orderly passing through at least two hydrogenation reaction zones connected in series, wherein in the material flowing direction, each hydrogenation reaction zone orderly comprises a hydro-upgrading catalyst bed layer, and a hydrodewaxing catalyst composite bed layer filled with a mixture of a hydrodewaxing catalyst and a hydro-refining catalyst; performing separation and fractionation of the reaction effluent from the last hydrogenation reaction zone to obtain the clean diesel oil product with a low condensation point, and a few light naphtha and liquefied gas products. The method of the invention reasonably combines and utilizes the temperature decrease of the hydrodewaxing process with the temperature increase of the hydro-refining and hydro-upgrading process, improves the diesel oil yield while producing diesel oil with a low condensation point and low sulfur, reduces the hot-spot temperature of the device, prolongs the running period, also reduces the cold hydrogen consumption or the combustion gas loss of a heating furnace, and saves operation cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

Method for producing hydrogenated diesel oil with low condensation point by gradation technology

ActiveCN103805251ALow costRealize comprehensive utilizationTreatment with hydrotreatment processesHydrogenation reactionSulfur

The invention discloses a method for producing hydrogenated diesel oil with a low condensation point by gradation technology. The method comprises the following steps: mixing a diesel oil raw material with hydrogen, orderly passing through at least two hydrogenation reaction zones connected in series, wherein in the material flowing direction, each hydrogenation reaction zone orderly comprises a hydro-refining hydro-upgrading catalyst composite bed layer filled with a mixture of a hydro-refining catalyst and a hydro-upgrading catalyst, and a hydrodewaxing catalyst bed layer; performing separation and fractionation of the reaction effluent from the last hydrogenation reaction zone to obtain the diesel oil product with a low condensation point. The method of the invention reasonably combines and utilizes the temperature decrease of the hydrodewaxing process with the temperature increase of the hydro-upgrading process, improves the diesel oil yield while producing diesel oil with a low condensation point and low sulfur, reduces the hot-spot temperature of the device, prolongs the running period, also reduces the cold hydrogen consumption or the combustion gas loss of a heating furnace, and saves operation cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

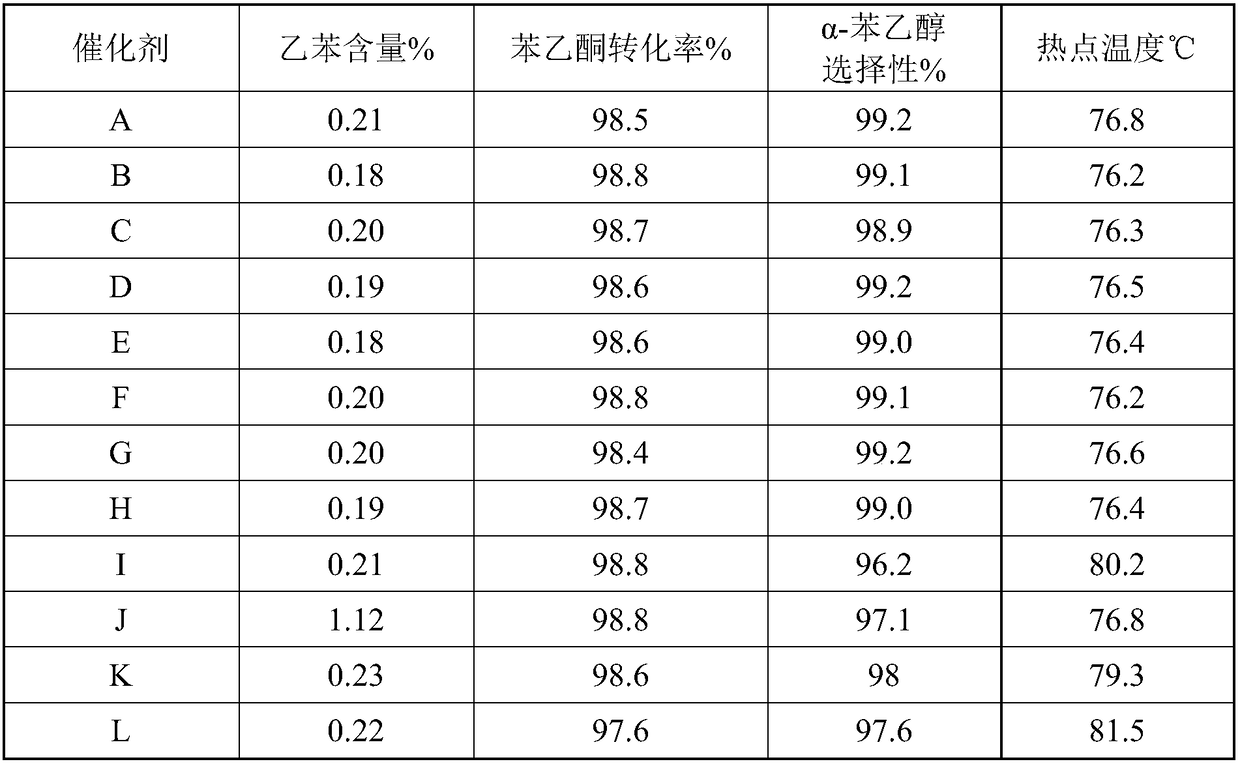

Method for preparing alpha-phenylethanol catalyst through hydrogenation of acetophenone and application

ActiveCN109482192AHigh activityAvoid filter effectsOrganic compound preparationHeterogenous catalyst chemical elementsPhenethyl alcoholSlurry

The invention relates to a method for preparing an alpha-phenylethanol catalyst through hydrogenation of acetophenone and application. The catalyst contains copper oxide, zinc oxide, silicon dioxide and bismuth oxide. The method of the catalyst is realized by virtue of a sub-step precipitation method and comprises the following steps: precipitating zinc salt and a precipitator at a certain temperature, and aging, so as to obtain slurry (1); adding a mixed solution of copper salt and bismuth salt as well as the precipitator into the slurry (1), carrying out coprecipitation, and aging, so as toobtain slurry (2); adding carrier silicon into the slurry (2), and uniformly stirring and mixing, so as to obtain slurry (3); filtering, washing, drying and roasting the slurry (3), so as to obtain catalyst powder; adding a certain amount of pore forming agents into the catalyst powder, and carrying out piece formation; and carrying out secondary roasting on the formed catalyst, so as to obtain the final catalyst. The catalyst prepared by virtue of the method is large in pore volume and aperture, good in mass transfer property and heat transfer property and high in activity and selectivity.

Owner:WANHUA CHEM GRP CO LTD

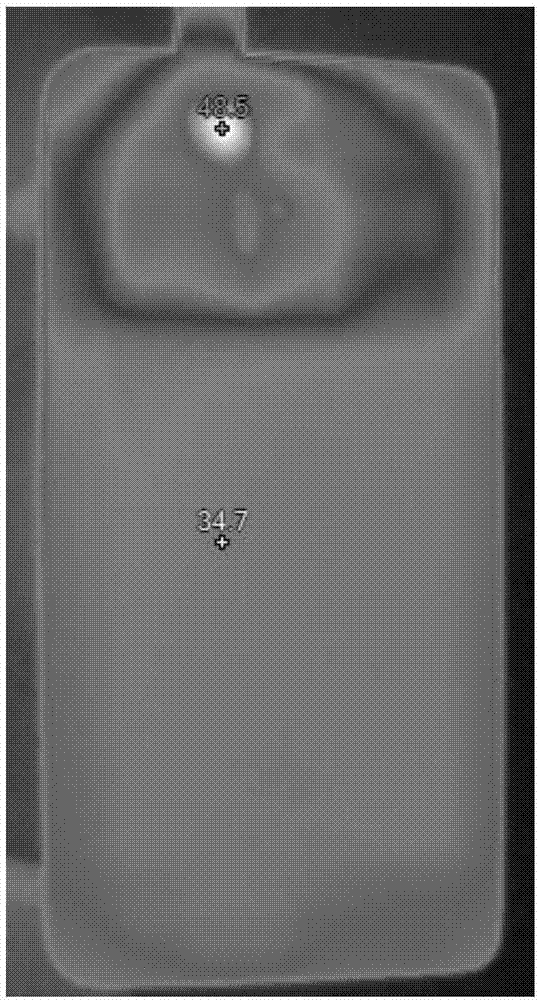

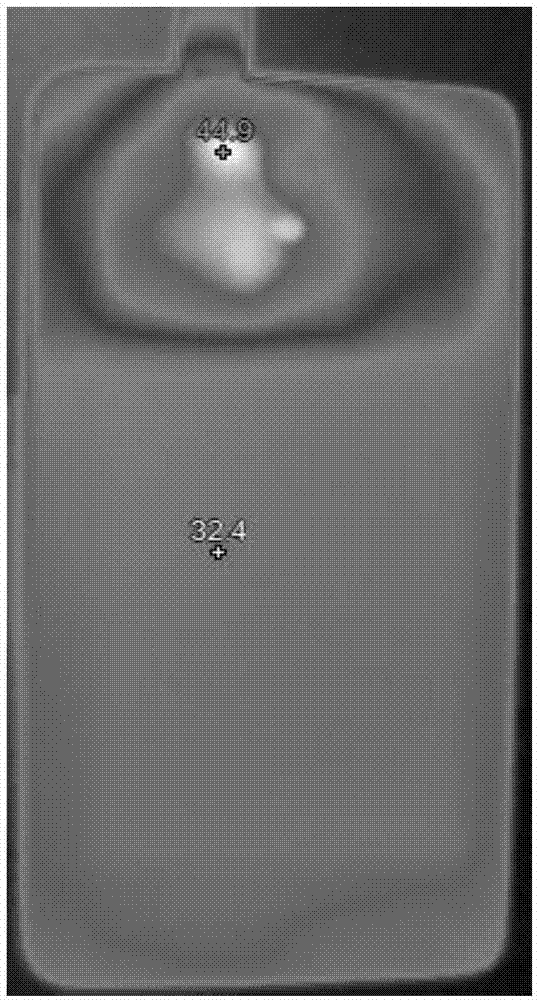

Structural component of mobile terminal and mobile terminal

Owner:上海博息电子科技有限公司

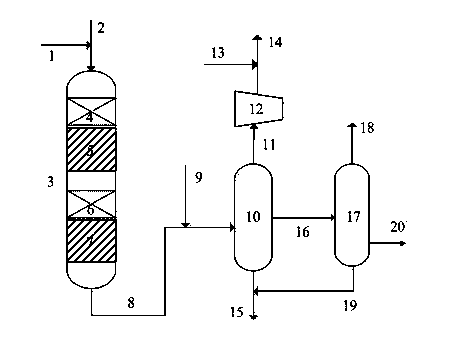

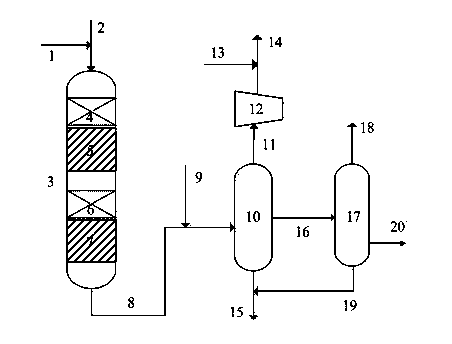

Preparing method for cyclohexane-1,2-dibasic diformate

ActiveCN106554278AGuaranteed complete hydrogenationReduce hot spot temperatureOrganic compound preparationCarboxylic acid esters preparationHydrogenation reactionDibasic ester

The invention relates to the field of hydrogenation for preparing cyclohexane-1,2-dibasic diformate, and discloses a preparing method for cyclohexane-1,2-dioctyl phthalate dibasic ester. The method comprises the steps that firstly, hydrogenation raw materials containing phthalic acid dibasic ester and H2 are subjected to first contact in a main hydrogenation reactor in the presence of a first catalyst, and first gas-liquid mixing fluid is obtained; secondly, the first gas-liquid mixing fluid is subjected to gas-liquid separation; thirdly, hydrogen is injected into main hydrogenation reaction liquid through holes with the average hole diameter being the nanometer size, the main hydrogenation reaction liquid is separated out in the second step, and second gas-liquid mixed fluid is obtained; fourthly, the second gas-liquid mixed fluid is subjected to second contact in a rear hydrogenation reactor in the presence of a second catalyst, and third gas-liquid mixed fluid is obtained; and fifthly, the third gas-liquid mixed fluid is subjected to gas-liquid separation. The method has the beneficial effects that the raw material conversion rate, the product selectivity and the cis-structure product content are high.

Owner:HUNAN CHANGLING PETROCHEM SCI & TECH DEV CO LTD

Hydroisomerization pour-point-depressing deep-coupling process for producing low-pour-point diesel oil

ActiveCN105087063AImprove combustion effectRealize cleaner productionTreatment with hydrotreatment processesIsomerizationHydrogenation reaction

The invention discloses a hydroisomerization pour-point-depressing deep-coupling process for producing low-pour-point diesel oil. The process comprises the following steps: mixing a diesel oil raw material and hydrogen; then successively allowing the mixture to pass through at least two tandem hydrogenation reaction zones, wherein each hydrogenation reaction zone successively includes a composite catalyst bed layer filled by a mixture of a hydrodewaxing catalyst and a hydro-upgrading isomerization pour-point-depressing catalyst, and a hydrofining catalyst bed layer according to a flow direction of the materials; and finally, subjecting an obtained reaction effluent of the last hydrogenation reaction zone to separation and fractionation so as to obtain the low-pour-point diesel oil. The method provided by the invention reasonably utilizes temperature rise in upgrading pour-point-depressing process and temperature drop in hydrodewaxing process, so clean low-pour-point diesel oil is produced; meanwhile, the yield and cetane number of the diesel oil are improved; hot-spot temperature of a device is reduced; and operation cycle is prolonged; moreover, consumption of cooled hydrogen and fuel gas loss of a heating furnace are reduced, and operation cost is saved.

Owner:CHINA PETROLEUM & CHEM CORP +1

Catalyst for selectively oxidizing tertiary butanol or isobutene to synthesize methyl acrylic aldehyde and its use

ActiveCN1314487CHigh activityImprove thermal conductivityPhysical/chemical process catalystsOrganic compound preparationGas phaseCatalytic oxidation

Owner:SHANGHAI HUAYI NEW MATERIAL

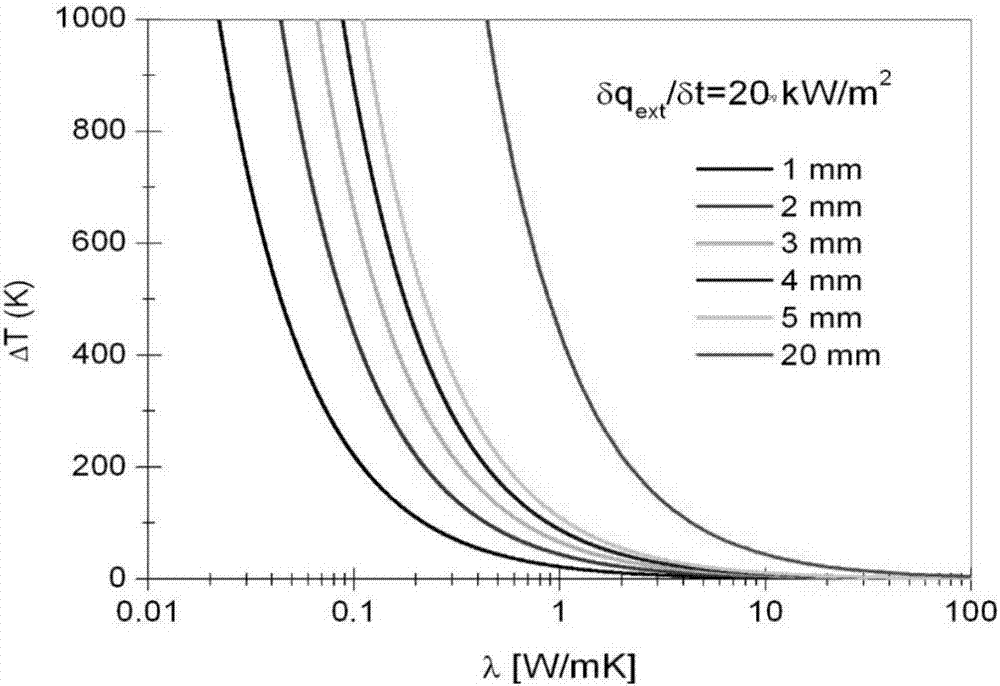

Thermal diffusion composite material

InactiveCN103448309AReduce volumeLow thermal conductivityNatural mineral layered productsRubber layered productsLiquid-crystal displayInsulation layer

The invention provides a thermal diffusion composite material. The composite material is compounded of a graphite film and a heat insulation layer through a compounding layer, wherein the heat insulation material is a compressible heat insulation material. According to the thermal diffusion composite material, the graphite film and the heat insulation effectively are effectively compounded to form a novel composite heat insulation material. The size of the heat insulation material is reduced through compressibility of the heat insulation material; meanwhile, the heat insulation material has a relatively low heat conduction coefficient, so that buffer is provided for thermal transmission of a product. The thermal diffusion composite material has the advantage that the compressibility of a heat conduction material is effectively realized by material compounding. Moreover, the thermal diffusion composite material can be used for effectively lowering a hot-spot temperature by 2 DEG C-3 DEG C, and also can be used for a LCD (Liquid Crystal Display) and an LED (Light-Emitting Diode) screen to avoid water ripples.

Owner:SUZHOU TIANMAI THERMAL TECH

Method for producing hydrogenated diesel oil with low freezing point

ActiveCN104611033AHigh yieldIncrease cetane numberTreatment with hydrotreatment processesHydrocarbon oils treatment productsHydrogenation reactionHeating furnace

The invention discloses a method for producing hydrogenated diesel oil with a low freezing point. The method comprises the following steps: mixing a diesel oil raw material with hydrogen, allowing the obtained mixture to sequentially go through at least two serially connected hydrogenation reaction zones, wherein the hydrogenation reaction zones sequentially comprise a pour point reduction modified catalyst composite bed layer filled with a hydrodewaxing catalyst and a hydroupgrading catalyst and a hydrodewaxing catalyst bed layer along a material flow direction; and separating a reaction effluent obtained from the last hydrogenation reaction zone, and fractioning to obtain a diesel oil product with a low freezing point. The method reasonably combines the temperature decrease of the hydrodewaxing process and the temperature rise of the hydroupgrading process, so the diesel oil with a low freezing point is produced, the yield and the cetane value of the diesel oil are improved, the hot spot temperature of a device is reduced, and the running period is prolonged; and the consumption of cold hydrogen or the combustion gas loss of a heating furnace is reduced, so the operating cost is saved.

Owner:CHINA PETROLEUM & CHEM CORP +1

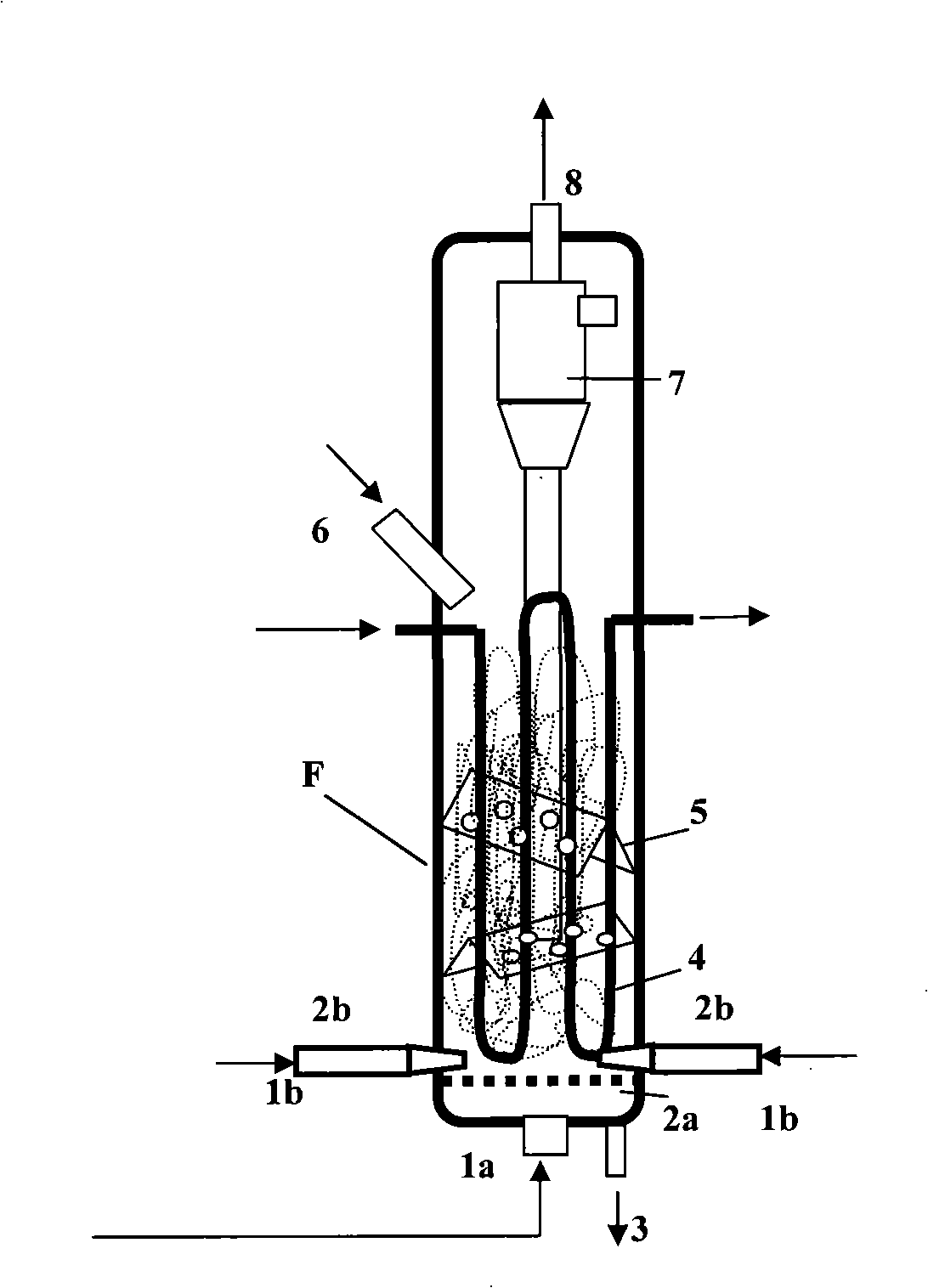

Inferior diesel pour-point depressing modification method

ActiveCN106675643ARealize comprehensive utilizationQuality assuranceTreatment with hydrotreatment processesHydrocarbon oils treatment productsHydrogenation reactionPour point

The invention discloses an inferior diesel pour-point depressing modification method, which comprises the following contents: (1) an inferior diesel material and a powdery hydrofining catalyst are fully mixed in a mixer to obtain a mixed feed of the catalyst and the raw oil; (2) the mixed feed and hydrogen enter a boiling-bed reactor from the bottom of a reactor filled with a mixture of a hydrodewaxing catalyst and a hydro-upgrading catalyst to undergo a hydrogenation reaction; (3) the reaction product is charged out of the top of the boiling-bed reactor and then enters a stable reactor to supplement hydrofining; and (4) the material undergoes solid-liquid separation, and a liquid phase enters a fractionating system so as to obtain a diesel product with high quality, low pour point, low sulfur content and high cetane number. According to the method, the backmixing characteristic of the boiling-bed reactor is fully utilized, and cooling and hydrofining of the hydrodewaxing process and temperature rising of the hydro-upgrading process are reasonably utilized. Therefore, the diesel with low pour point and ultra-low sulfur content is produced, cetane number is raised, hot-spot temperature of the device is reduced, running period is prolonged, and operation expenses are saved.

Owner:CHINA PETROLEUM & CHEM CORP +1

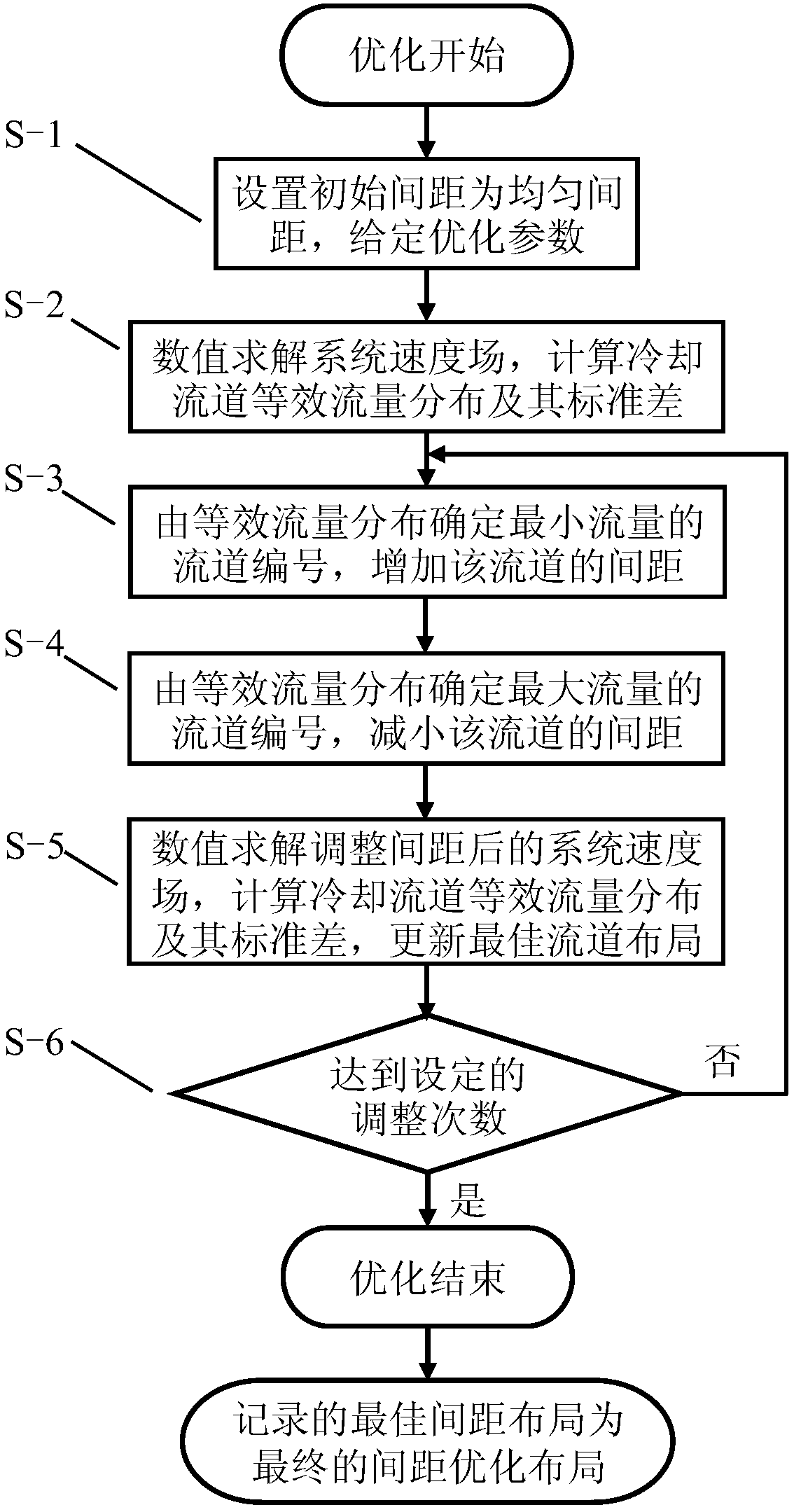

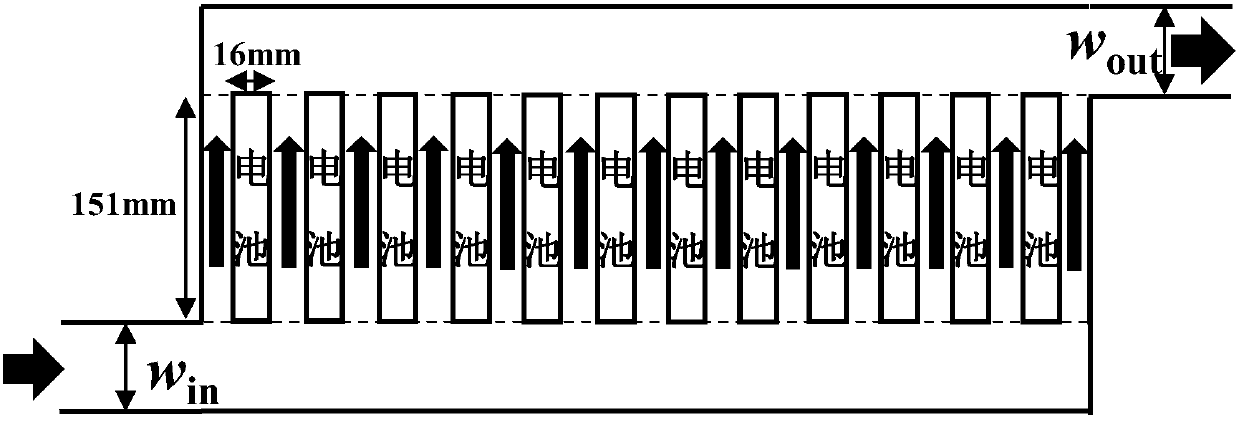

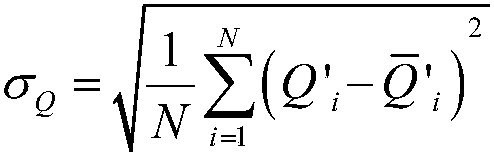

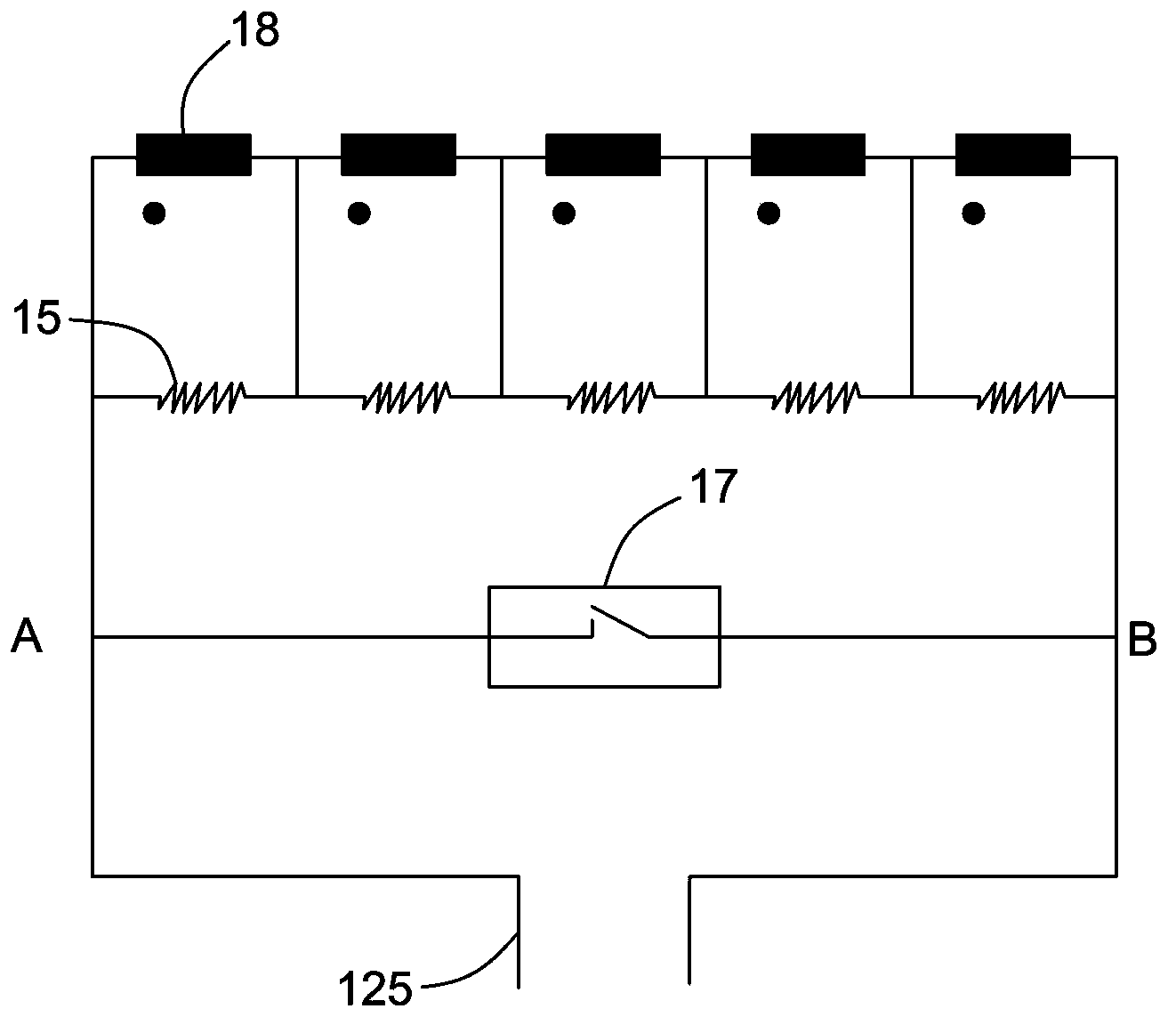

Rapid optimization method for power battery air cooling system runner interval

ActiveCN108038261AIncreased runner spacingReduced runner spacingSecondary cellsForecastingPower batteryMaximum flux

The invention discloses a rapid optimization method for a power battery air cooling system runner interval. The method comprises the steps that beginning from the uniform runner interval, velocity distribution of an air cooling system is solved through numerical values, by analyzing the flow distribution between cooling runners, the runner with the minimum flow and the runner with the maximum floware determined, then, the interval of the runner with the minimum flow is increased, and the interval of the runner with the maximum flow is decreased; speed distribution of the system is calculatedagain every time the runner interval is adjusted, and therefore the next runner interval adjustment is performed; when the frequency for runner interval adjustment reaches the set frequency, the layout of the runner interval with the minimum cooling runner equivalent flow standard deviation in the process is adjusted, and the final runner interval optimization result is obtained. The rapid optimization method has the advantages of being simple in optimization process, high in optimization speed, good in performance index, good in expansibility, high in practicability and the like.

Owner:SOUTH CHINA UNIV OF TECH

Method for producing diesel oil with low condensation point by gradation technology

ActiveCN103805259AGuaranteed yieldRealize comprehensive utilizationTreatment with hydrotreatment processesFractionationChemistry

The invention discloses a method for producing diesel oil with a low condensation point by gradation technology. The method comprises the following steps: mixing a diesel oil raw material with hydrogen, orderly passing through at least two hydrogenation reaction zones connected in series, wherein in the material flowing direction, each hydrogenation reaction zone orderly comprises a hydro-upgrading isodewaxing catalyst bed layer, and a dewaxing catalyst composite bed layer filled with a mixture of a hydro-upgrading isodewaxing catalyst and a hydrodewaxing catalyst; performing separation and fractionation of the reaction effluent from the last hydrogenation reaction zone to obtain the diesel oil product with a low condensation point. The method of the invention reasonably combines and utilizes the temperature increase of the hydro-upgrading dewaxing process with the temperature decrease of the hydrodewaxing process, improves the diesel oil yield and the cetane value while producing diesel oil with a low condensation point and low sulfur, reduces the hot-spot temperature of the device, prolongs the running period, also reduces the cold hydrogen consumption or the combustion gas loss of a heating furnace, and saves operation cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

Preparation method of 1,3-propylene glycol

InactiveCN108358750AReduce hot spot temperatureReduced acetal impurity contentOrganic compound preparationHydroxy compound preparationHydrogenation reactionAqueous solution

The invention provides a preparation method of 1,3-propylene glycol. The preparation method comprises the following steps: providing an aqueous solution of 3-hydroxypropionaldehyde with the mass concentration of 8 to 13 percent; mixing hydrogen and the aqueous solution of 3-hydroxypropionaldehyde, and successively performing the one-stage hydrogenation reaction and two-stage hydrogenation reactionto obtain a two-stage hydrogenated product; and circulating a part of the two-stage hydrogenated product to the one-stage hydrogenation reaction. According to the preparation method of 1,3-propyleneglycol, part of the two-stage hydrogenated product is circulated to the one-stage hydrogenation reaction to absorb the reaction heat, so that the hot-spot temperature of the first hydrogenation reaction can be reduced, the content of acetal impurities in the product can be effectively reduced, and the selectivity of the hydrogenation reaction can be improved.

Owner:王鹏飞

Selective hydrogenation method for C5 fraction of ethylene cracking by-product

ActiveCN102911714ASolve the problem of easy aggregationProblems that affect the life cycleRefining by selective hydrogenationAlkaneAlkadiene

The invention discloses a selective hydrogenation method for C5 fraction of an ethylene cracking by-product. The selective hydrogenation method comprises the following steps of (1) performing selective hydrogenation by using the C5 fraction of the ethylene cracking by-product as a raw material to remove alkadiene and alkyne, wherein catalyst is arranged in 3-5 reaction sections along flow direction of reaction materials; catalyst volume content in each reaction section is increased by 5-30% than that in the former adjacent reaction section successively; the amount of the catalyst in a first section is 8%-20% of a total volume of the catalyst; and the amount of the catalyst in last section is 40%-65% of the total volume of the catalyst; (2) adding a diluent in the raw material, wherein the diluent is a saturated alkane; and (3) adding a polymerization inhibitor selectively in the raw material. The method can remove alkadiene and alkyne from the C5 fraction with high content of alkadiene and alkyne via selective hydrogenation, simultaneously solves the easy coking problem of the catalyst, and can guarantee that a reaction apparatus runs stably for a long time.

Owner:CHINA PETROLEUM & CHEM CORP +1

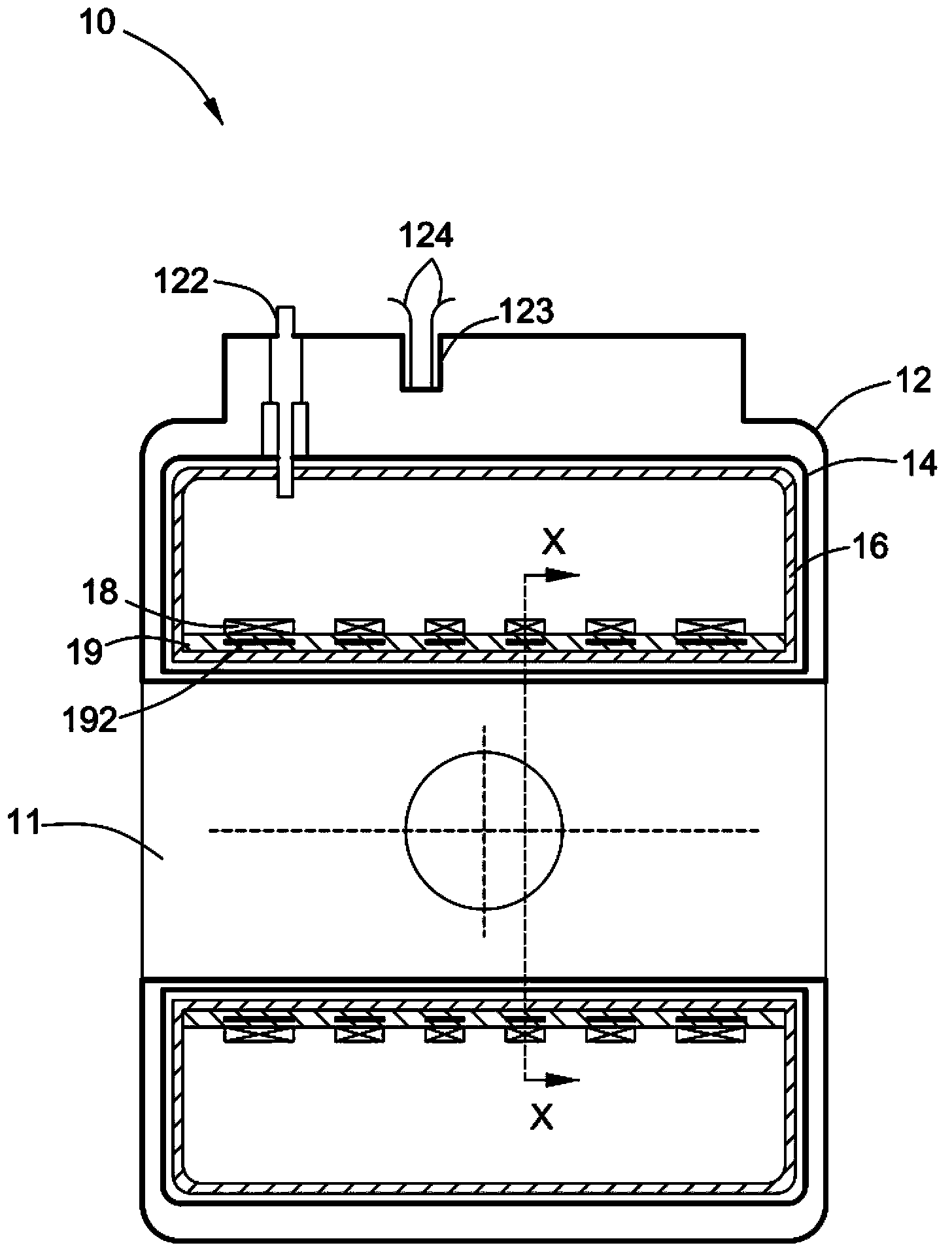

Superconducting magnet system

ActiveCN103700461AReduce hot spot temperatureReduce load pressureSuperconducting magnets/coilsElectromagnetic couplingHeat conducting

The invention relates to a superconducting magnet system, which comprises a coil support structure, a plurality of superconducting coils and a plurality of conducting rings, wherein the superconducting coils are supported and fixed through the coil supporting structure, and the conducting rings have electric conducting and heat conducting performance and are internally embedded inside the coil support structure. Each conducting ring per se forms a short circuit connecting structure of a closed loop in the circumferential direction, and the conducting rings and the superconducting coils have the electromagnetic coupling setting.

Owner:GENERAL ELECTRIC CO

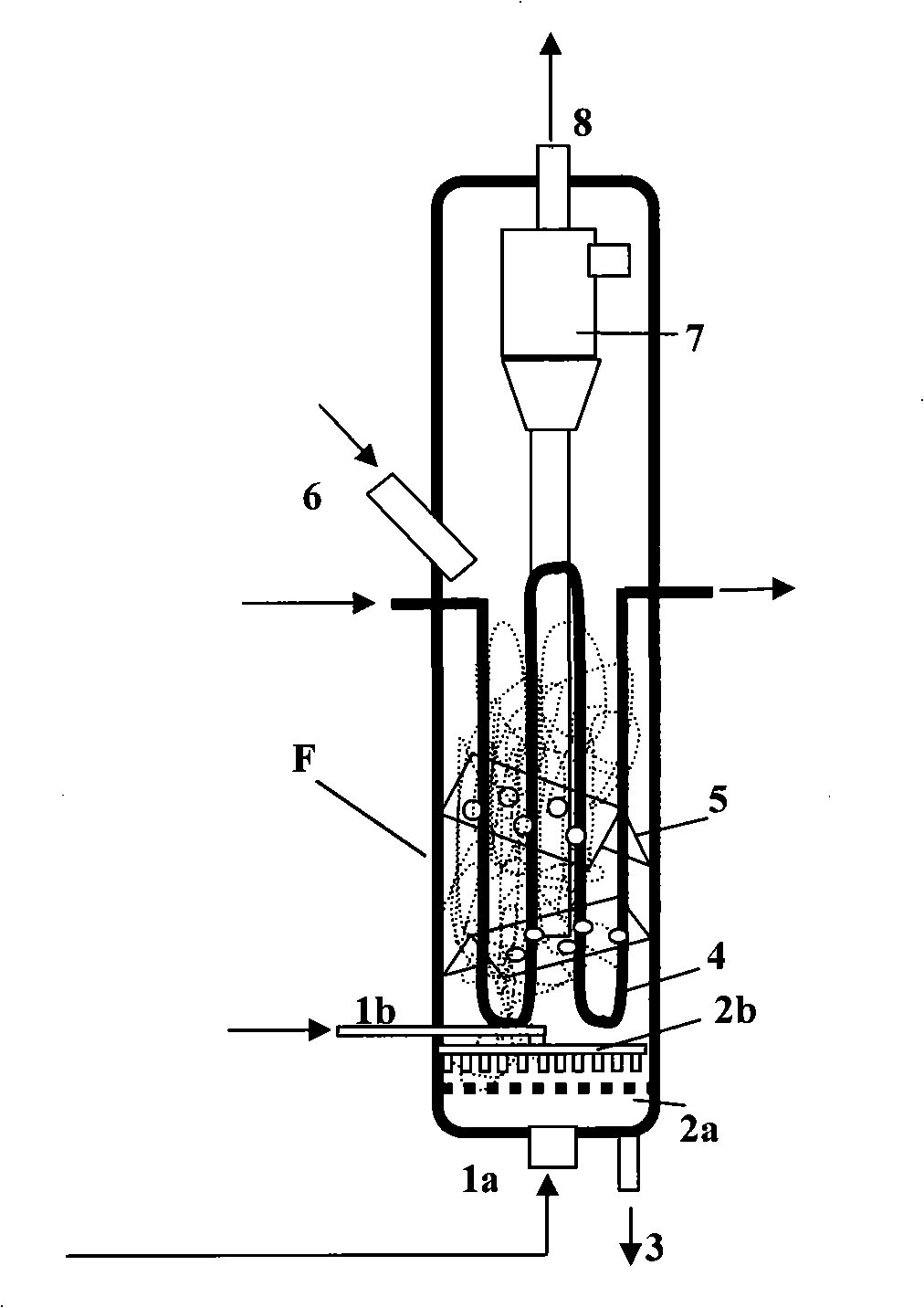

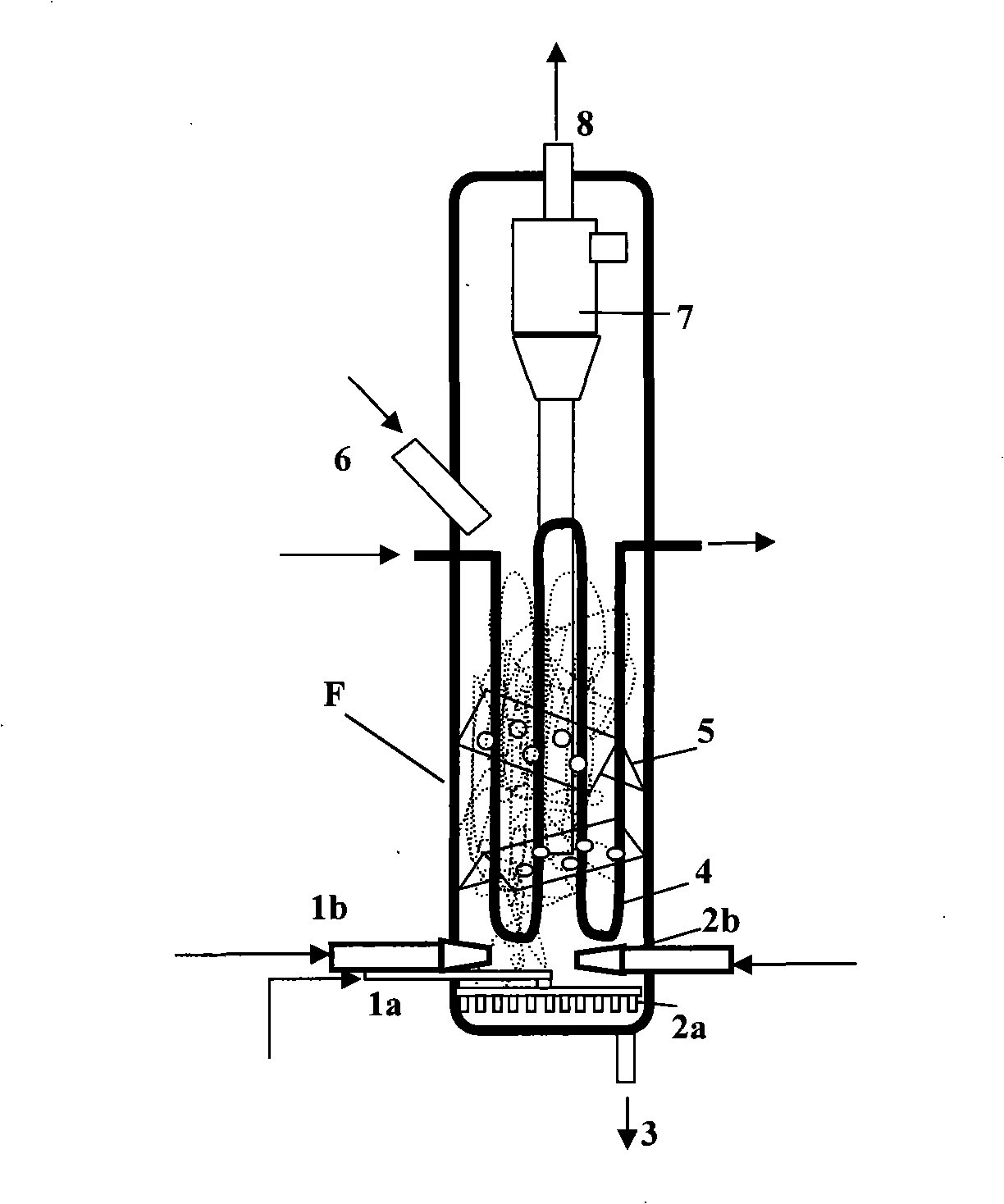

Gas distributor in chloroethylene synthesis fluidized bed and chloroethylene synthetic method

InactiveCN101328107AExtend your lifeReduce manufacturing costPreparation by halogen halide additionChemical/physical processesSynthesis methodsDistributor

The invention particularly relates to a gas distributor of the vinyl chloride synthesis fluidized bed and a synthesis method of vinyl chloride belonging to the field of chemical equipment and technology. Double distributors or one distributor and one group of gas(liquid) nozzles are arranged on the bottom of the fluidized bed. The invention also discloses a method for preparing vinyl chloride by reacting hydrogen chloride with acetylene in a fluidized bed reactor containing the distributor, which comprises controlling the feed temperature, the ratio of composition and flow of the double distributors or one distributor and a group of gas(liquid) nozzles, adjusting the temperature of the gas distributor area by of the cold shock principle of the low temperature gas(liquid). The method of the invention has advantages that the temperature control is sensitive and convenient, the highest and average temperature of the gas distributor area are reduced, the active component loss on the catalyst is inhibited and the coke on the catalyst is reduced, thereby prolonging the catalyst service life, improving the purity of the vinyl chloride product and simplifying the product exhaust post treatment with a low cost.

Owner:TSINGHUA UNIV

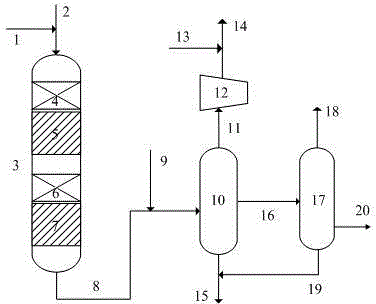

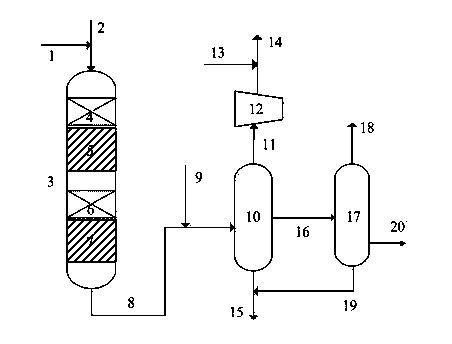

Method for prolonging running period of acrylic acid device

InactiveCN104193582AReduce hot spot temperatureReduce the use effectCatalyst protectionOrganic compound preparationPolymer scienceHeat resistance

The invention provides a method for prolonging the running period of an acrylic acid device. The method comprises the following steps: loading a catalyst without diluting by use of an inert filler, arranging coated catalyst bed layers having different heat resistances in a tube fixed-bed reactor according to the heat resistance in the axial direction of the reactor; and loading a coated catalyst relatively low in heat resistance in a position near the outlet of a reaction tube, and then orderly loading coated catalysts relatively high in heat resistance in such a manner that the coated catalyst close to the inlet of the reaction tube has the highest heat resistance, wherein the coated catalysts having different heat resistances are catalysts the inner cores of which are high-activity composite oxides with heat-resistant ceramic balls, and are obtained by controlling the sizes of the heat-resistant ceramic balls and the coating ratio of an active ingredient. Due to the adopted method, not only is the running period of the acrylic acid device prolonged, but also the production device has relatively high reaction efficiency.

Owner:CHINA NAT OFFSHORE OIL CORP +3

Catalyst for selectively oxidizing methyl acrylic aldehyde to synthesize methyl propenoic acid and its use

ActiveCN100490973CHigh reactivityHigh selectivityPhysical/chemical process catalystsOrganic compound preparationHeteropoly acidGas phase

Owner:SHANGHAI HUAYI NEW MATERIAL

Lubricating oil base oil production method

ActiveCN104611044ALow aromatic contentReduce consumptionTreatment with hydrotreatment processesLubricant compositionFractionationWhite oil

The present invention discloses a lubricating oil base oil production method. According to the lubricating oil base oil production method of the present invention, a wax oil raw material and hydrogen gas are mixed and then sequentially pass through at least two hydrogenation reaction zones connected in series, wherein each hydrogenation reaction zone sequentially comprises a composite catalyst bed layer filled with a hydrodewaxing catalyst and a hydrocracking catalyst in a mixed manner and a hydrodewaxing catalyst bed layer according to the material flowing direction, and the reaction effluent obtained from the last hydrogenation reaction zone is subjected to separation and fractionation to obtain the lubricating oil base oil, the white oil and other products. With the method of the present invention, the temperature decrease during the hydrodewaxing process and the temperature increase during the hydrogenation process are subjected to reasonable combination utilization, such that the low freezing point lubricating oil base oil is produced while the viscosity index is increased, the hot spot temperature of the device is reduced, and the operation period is prolonged; and the cold hydrogen consumption or the heating furnace fuel gas loss is reduced, and the operating cost is saved.

Owner:CHINA PETROLEUM & CHEM CORP +1

Method for producing hydrogenated diesel oil with low condensation point by catalyst gradation technology

ActiveCN103805255AReduce hot spot temperatureGuaranteed yieldTreatment with hydrotreatment processesHydrogenation reactionSulfur

The invention discloses a Method for producing hydrogenated diesel oil with a low condensation point by catalyst gradation technology. The method comprises the following steps: mixing diesel oil with hydrogen, orderly passing through at least two hydrogenation reaction zones connected in series, wherein in the material flowing direction, each hydrogenation reaction zone orderly comprises a dewaxing hydro-upgrading catalyst composite bed layer filled with a mixture of a hydro-upgrading isodewaxing catalyst and a hydro-upgrading catalyst, and a hydrodewaxing catalyst bed layer; performing separation and fractionation of the reaction effluent from the last hydrogenation reaction zone to obtain the diesel oil product with a low condensation point. The method of the invention reasonably combines and utilizes the temperature increase of the hydro-refining and hydro-upgrading dewaxing process with the temperature decrease of the hydrodewaxing process, improves the diesel oil yield and the cetane value while producing diesel oil with a low condensation point and low sulfur, reduces the hot-spot temperature of the device, prolongs the running period, also reduces the cold hydrogen consumption or the combustion gas loss of a heating furnace, and saves operation cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

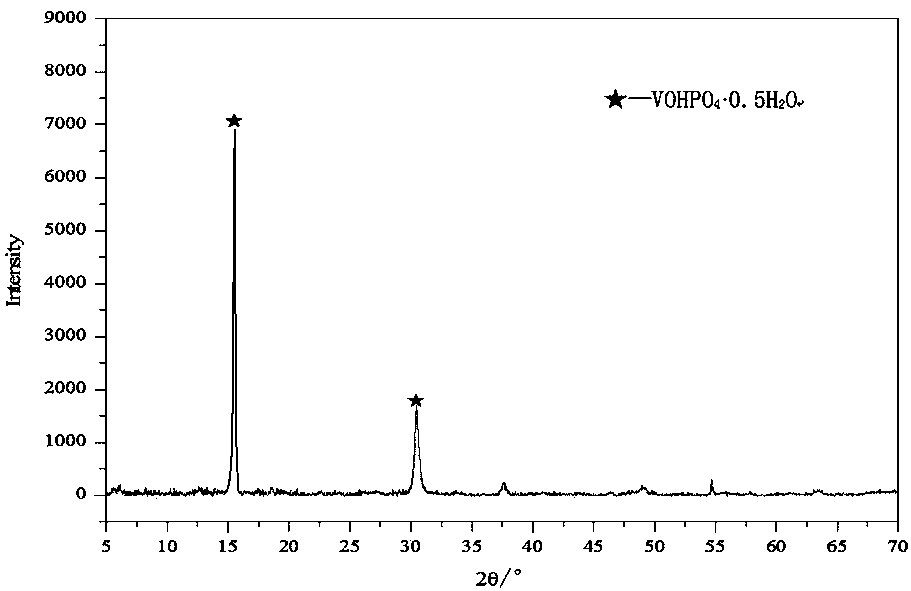

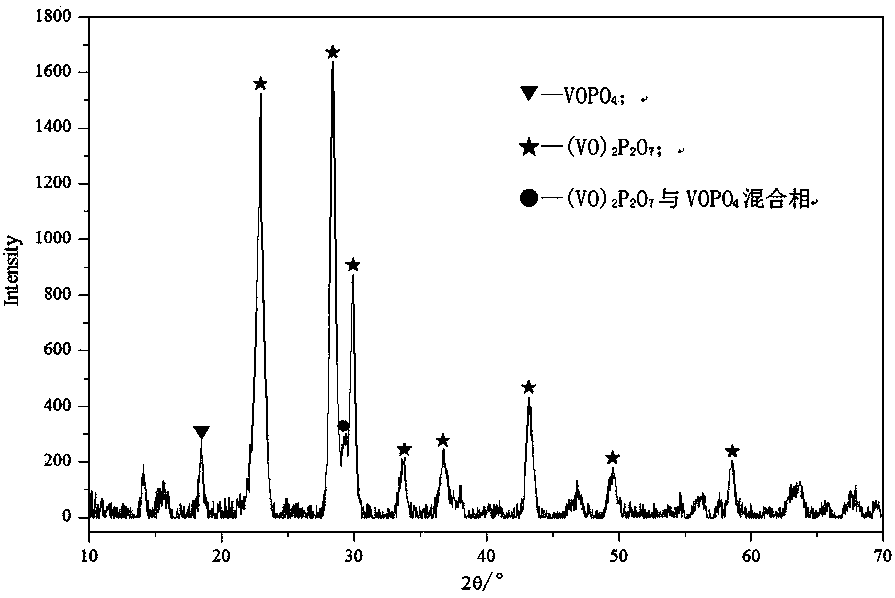

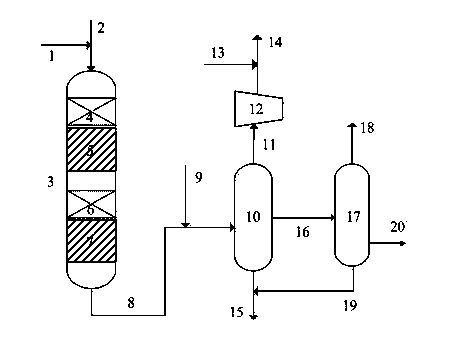

Catalyst grading method for preparation of maleic anhydride from n-butane by oxidation

ActiveCN108101872APromote conversionIncrease volume fractionOrganic chemistryPhysical/chemical process catalystsSide reactionButane

The invention discloses a catalyst grading method for preparation of maleic anhydride from n-butane by oxidation. N-butane is mixed with air, and obtained mixed reaction gas flows in parallel throughthree or more vanadium phosphorus oxide catalyst beds connected in series, and is contacted with a vanadium phosphorus oxide catalyst for reaction under the oxidation reaction condition, wherein according to the contact sequence with the mixed reaction gas, the three or more catalyst beds connected in series perform graded loading according to the trend of the P / V molar ratio of the catalyst beingfirstly low, high and then low, so that activity distribution of the catalyst is balanced, and the activity of the catalyst is fully exerted. With the method, the n-butane concentration in feed can be increased, the reaction hot spot of the beds is reduced, temperature distribution of the beds is uniform, occurrence of side reactions is effectively inhibited, selectivity of a product is improved,and the yield of the product maleic anhydride is increased.

Owner:CHINA PETROLEUM & CHEM CORP +1

Production method of clean diesel oil with low condensation point

ActiveCN103805244ARealize comprehensive utilizationGuaranteed yieldTreatment with hydrotreatment processesNaphthaSulfur

The invention discloses a production method of clean diesel oil with a low condensation point. The method comprises the following steps: mixing diesel oil with hydrogen, orderly passing through at least two hydrogenation reaction zones connected in series, wherein in the material flowing direction, each hydrogenation reaction zone orderly comprises a hydro-refining dewaxing catalyst composite bed layer filled with a mixture of a hydrodewaxing catalyst and a hydro-refining catalyst, and a hydro-upgrading catalyst bed layer; performing separation and fractionation of the reaction effluent from the last hydrogenation reaction zone to obtain the clean diesel oil product with a low condensation point, and a little light naphtha and liquefied gas. The method of the invention reasonably combines and utilizes the temperature decrease of the hydrodewaxing process with the temperature increase of the hydro-refining and hydro-upgrading process, improves the diesel oil yield while producing diesel oil with a low condensation point and low sulfur, reduces the hot-spot temperature of the device, prolongs the running period, also reduces the cold hydrogen consumption or the combustion gas loss of a heating furnace, and saves operation cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

Cooling structure design method of high-pressure turbine guide cooling blade margin plate

ActiveCN113202567AExtend your lifeReduce hot spot temperatureEfficient propulsion technologiesStatorsCold airCooling effect

The invention belongs to the field of aero-engine blades, and particularly relates to a cooling structure design method for a high-pressure turbine guide cooling blade margin plate. The cooling structure design method for the high-pressure turbine guide cooling blade margin plate comprises the steps that firstly, the margin plate is partitioned into a cold air introduction area and a non-cold air introduction area according to the air introduction position of the margin plate and the position of a vertical plate; secondly, an impact and air film combined cooling structure is designed in the cold air introduction area of the margin plate; thirdly, a turbulent flow column and air film combined cooling structure is designed in the non-cold air introduction area of the margin plate; fourthly, gas film cooling structures are designed on the fuel gas side surface of the margin plate and a blade body close to the margin plate; and fifthly, variable-radius fillets are arranged on the connecting sections of the margin plate and the blade body along a blade profile. According to the cooling structure design method for the high-pressure turbine guide cooling blade margin plate, a combined cooling mode is adopted for cooling the wall face of the high-pressure turbine guide blade margin plate, the hot-spot temperature of the margin plate can be reduced, the cooling effect of the blade margin plate can be improved, and the service life of blades can be prolonged.

Owner:AECC SHENYANG ENGINE RES INST

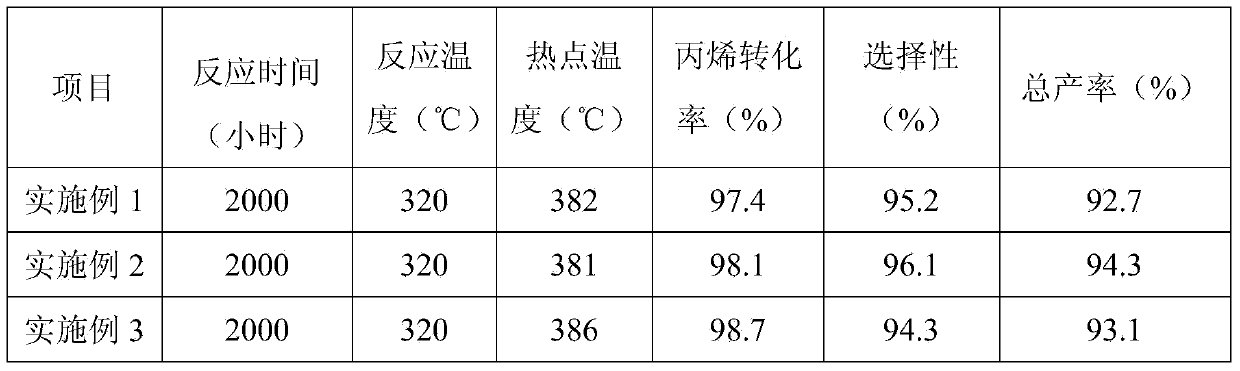

Catalyst and preparation method thereof

ActiveCN103157484AReduce hot spot temperatureExtended service lifeOrganic compound preparationCarbonyl compound preparationComposite oxideOxygen atom

Disclosed are a catalyst composition, and a preparation method and application thereof. The catalyst composition comprises the following components: a) 10-45 wt% of silicon powder; and b) 55-90 wt% of a composite oxide having a following formula of Mo12BibFecCodXeYfZgOh, wherein X is at least one element selected from the group consisting of W, Sb, As, P, Ni, Sn and Pb; Y is at least one element selected from the group consisting of Zn, Cr, Mn, Ru, Ag, Pd and Ru; Z is at least one element selected from the group consisting of alkali metals or alkaline earth metals; b is 0.1-7; c is 0.5-8; d+e is 0.5-20; f is 0-1; g is 0-2; and h is the number of oxygen atoms satisfying the oxidation state of the elements.

Owner:SHANGHAI HUAYI NEW MATERIAL

Catalyst for preparing phthalic anhydride as well as preparation method and application thereof

ActiveCN108097282AReduce churnGuaranteed performanceOrganic chemistryCatalyst activation/preparationPhosphomolybdic acidControlled release

The invention relates to a catalyst for preparing phthalic anhydride as well as a preparation method and application thereof and is especially suitable for ortho-xylene or naphthalene gas phase oxidation to prepare the phthalic anhydride. The catalyst for preparing the phthalic anhydride is prepared from active ingredients, wherein the active ingredients are prepared from 0.01 to 20% of polyoxometalate and the balance of oxide or salt by mass percent, wherein the polyoxometalate is of a keggin structure and is prepared from any one or combination of any two of tungstophoric acid cesium and phosphomolybdic acid cesium according to any proportion; the oxide is at least one of V2O5, TiO2, Sb2O3, P2O5, Cs2O, Fe2O3, WO2, MoO3, SnO2 or Ag2O. The catalyst disclosed by the invention can reduce a reaction hot-spot temperature through a decomposing and controlled-release effect of the polyoxometalate and an adjusting effect to a catalyst acidity; thus, selectivity of the catalyst is improved, and service life of the catalyst is prolonged.

Owner:DALIAN DRAGON WIN CATALYTIC