Method for monitoring silicon chip injection temperature

A silicon wafer and post-implantation technology, applied in semiconductor/solid-state device testing/measurement, electrical components, circuits, etc., can solve problems such as unable to monitor ion implantation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

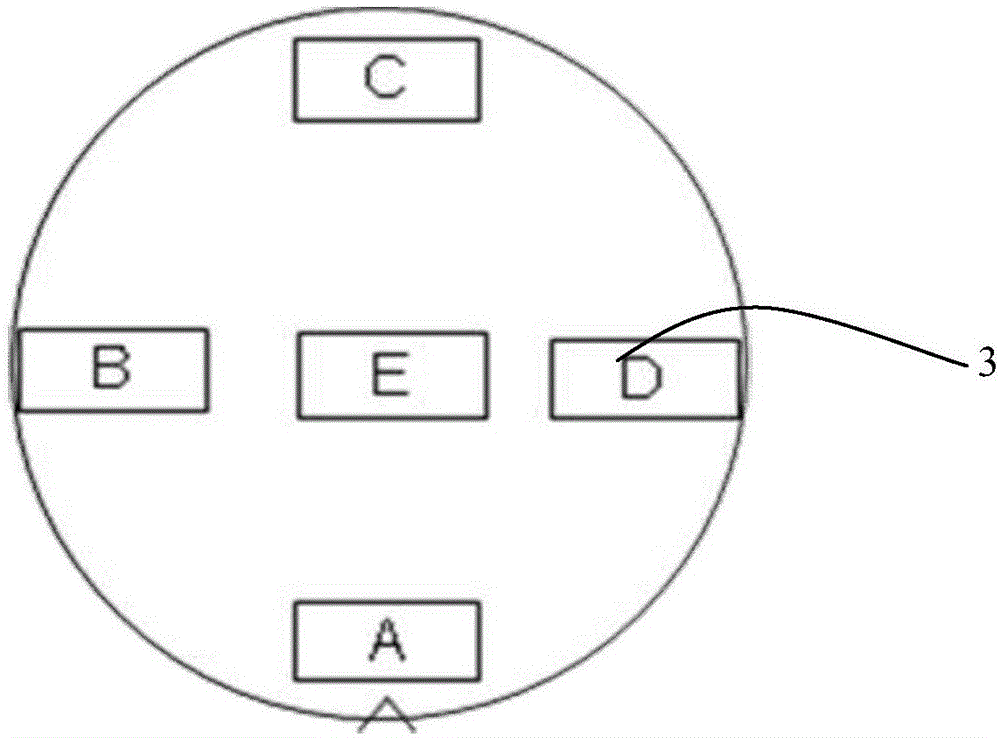

[0038] Such as image 3 As shown, polysilicon is a commonly used material in semiconductor manufacturing. Its manufacturing cost is low, and it can be grown by CVD (chemical vapor deposition), with good uniformity and high yield; polysilicon film can be peeled off by wet chemical solution tank and then Growing, silicon wafers can be recycled and used repeatedly.

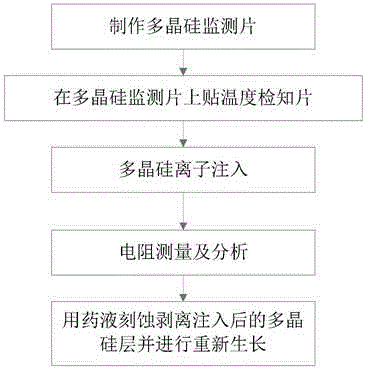

[0039] Such as Figure 6 As shown, the method for monitoring the temperature of implanted silicon wafer in a preferred embodiment of the present invention comprises the following steps:

[0040] Step 1, making a polysilicon monitoring chip. Deposit a layer of silicon oxide on the silicon substrate, and then grow a layer of 3000 angstrom polysilicon layer. The polysilicon layer can be grown by CVD (chemical vapor deposition). The working temperature of the chemical vapor deposition method can be controlled between 500°C and 700°C. Polysilicon ions are uniformly deposited on the oxide layer in the physical vapor dep...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More