Shortest-distance-based spacing test results classifying method for use in integrated circuit layout and flat panel display layout

A technology with the shortest distance and inspection results, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of delaying the layout design process, manual classification and inspection results, and low work efficiency, to speed up manual classification and screening, The effect of assisting efficient classification and improving image inspection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] This section details the preferred way of carrying out the invention.

[0026] The preferred way to realize the invention corresponds to the main technical solution, including the following three aspects:

[0027] First, the distance check results before merging and the calculation of the shortest distance.

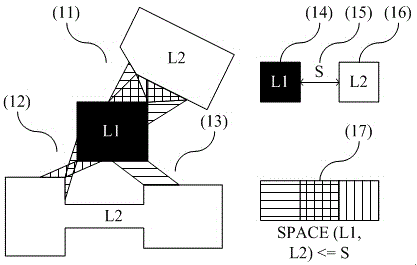

[0028] refer to figure 1 , Figures (11) (12) (13) represent a part of the circuit layout and the spacing check results before merging, and the right figure (14) (15) (16) (17) defines the spacing checking rules:

[0029] As shown in (14), the black geometric figure is an input layer L1 for spacing check;

[0030] As shown in (15), the white geometry is another input layer L2 for spacing check;

[0031] As shown in (16), S is the distance check size, when the distance between the L1 layer graphics and the L2 layer graphics is less than or equal to S, the result is output;

[0032] As shown in (17), the shadow geometry is the output result layer of the spacing ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More