Three-valued sensitive amplifier and SRAM array implementing same

一种灵敏放大器、阵列的技术,应用在灵敏放大器领域,能够解决延时大、漏电流和极间电容大、芯片成品率低等问题,达到功耗降低、工作速度提高的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

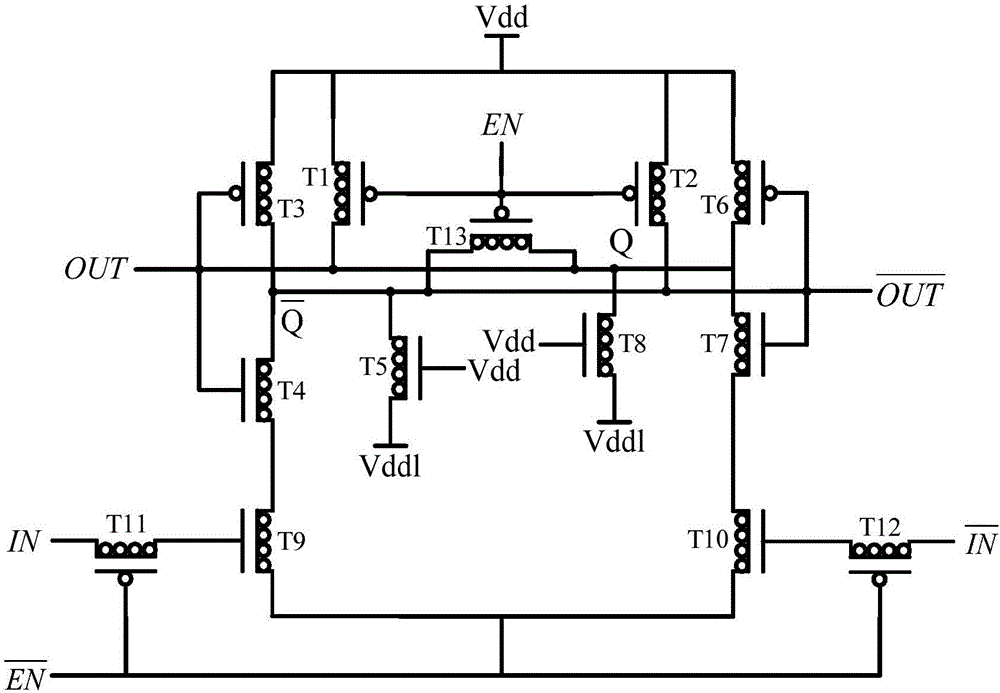

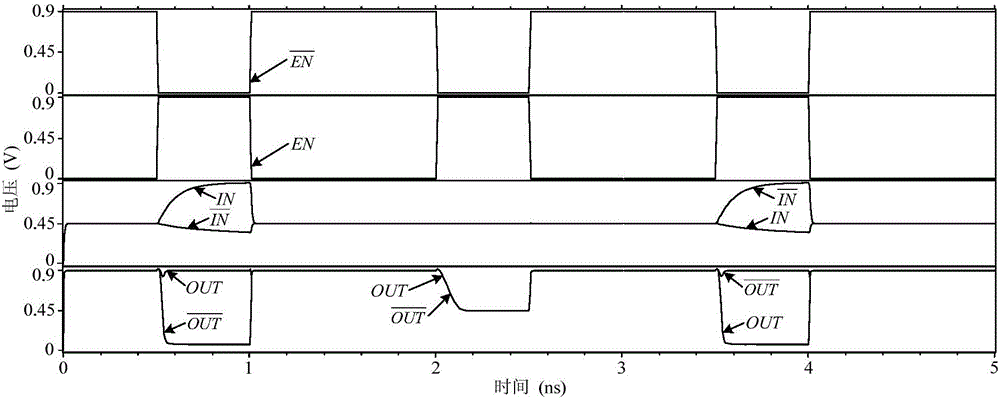

[0021] Example: such as figure 1As shown, a three-valued sensitive amplifier includes a first CNFET tube T1, a second CNFET tube T2, a third CNFET tube T3, a fourth CNFET tube T4, a fifth CNFET tube T5, a sixth CNFET tube T6, and a seventh CNFET tube Tube T7, eighth CNFET tube T8, ninth CNFET tube T9, tenth CNFET tube T10, eleventh CNFET tube T11, twelfth CNFET tube T12 and thirteenth CNFET tube T13; first CNFET tube T1, second The CNFET tube T2, the third CNFET tube T3, the sixth CNFET tube T6, the eleventh CNFET tube T11, the twelfth CNFET tube T12 and the thirteenth CNFET tube T13 are all P-type CNFET tubes, the fourth CNFET tube T4, the The fifth CNFET tube T5, the seventh CNFET tube T7, the eighth CNFET tube T8, the ninth CNFET tube T9 and the tenth CNFET tube T10 are all N-type CNFET tubes; the source of the first CNFET tube T1 and the source of the second CNFET tube T2 The source, the source of the third CNFET transistor T3, the gate of the fifth CNFET transistor T5, t...

Embodiment 1

[0035] Embodiment one: if figure 1 and Figure 5As shown, a SRAM array implemented by a three-value sense amplifier, including a three-value sense amplifier, a three-value storage array, a first inverter G1, a second inverter G2, a third inverter G3, and a fourth inverter device G4, the fourteenth CNFET tube T14, the fifteenth CNFET tube T15, the sixteenth CNFET tube T16, the seventeenth CNFET tube T17, the eighteenth CNFET tube T18, and the nineteenth CNFET tube T19; the memory array has a bit line and anti-phase line, the fourteenth CNFET tube T14, the fifteenth CNFET tube T15, the sixteenth CNFET tube T16 and the eighteenth CNFET tube T18 are all P-type CNFET tubes, the seventeenth CNFET tube T17 and the nineteenth CNFET tube T17 The CNFET tubes T19 are all N-type CNFET tubes; the three-valued sensitive amplifier includes the first CNFET tube T1, the second CNFET tube T2, the third CNFET tube T3, the fourth CNFET tube T4, the fifth CNFET tube T5, and the sixth CNFET tube T...

Embodiment 2

[0036] Embodiment two: if figure 1 and Figure 5 As shown, a SRAM array implemented by a three-value sense amplifier, including a three-value sense amplifier, a three-value storage array, a first inverter G1, a second inverter G2, a third inverter G3, and a fourth inverter device G4, the fourteenth CNFET tube T14, the fifteenth CNFET tube T15, the sixteenth CNFET tube T16, the seventeenth CNFET tube T17, the eighteenth CNFET tube T18, and the nineteenth CNFET tube T19; the memory array has a bit line and anti-phase line, the fourteenth CNFET tube T14, the fifteenth CNFET tube T15, the sixteenth CNFET tube T16 and the eighteenth CNFET tube T18 are all P-type CNFET tubes, the seventeenth CNFET tube T17 and the nineteenth CNFET tube T17 The CNFET tubes T19 are all N-type CNFET tubes; the three-valued sensitive amplifier includes the first CNFET tube T1, the second CNFET tube T2, the third CNFET tube T3, the fourth CNFET tube T4, the fifth CNFET tube T5, and the sixth CNFET tube ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More