On-chip bus test system based on Tbus bus standard

An on-chip bus, test system technology, used in faulty hardware testing methods, error detection/correction, detection of faulty computer hardware, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

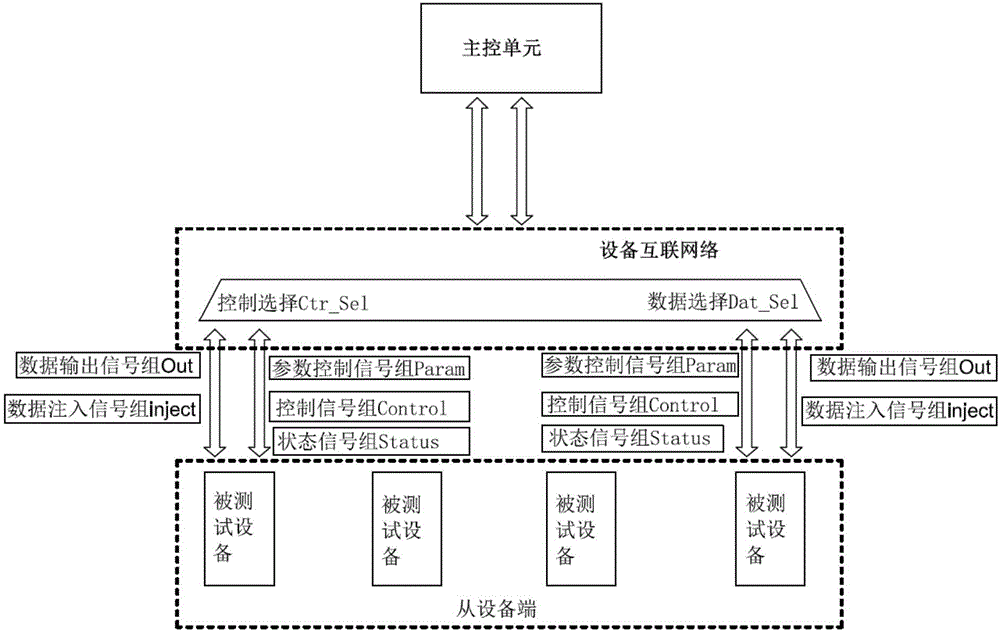

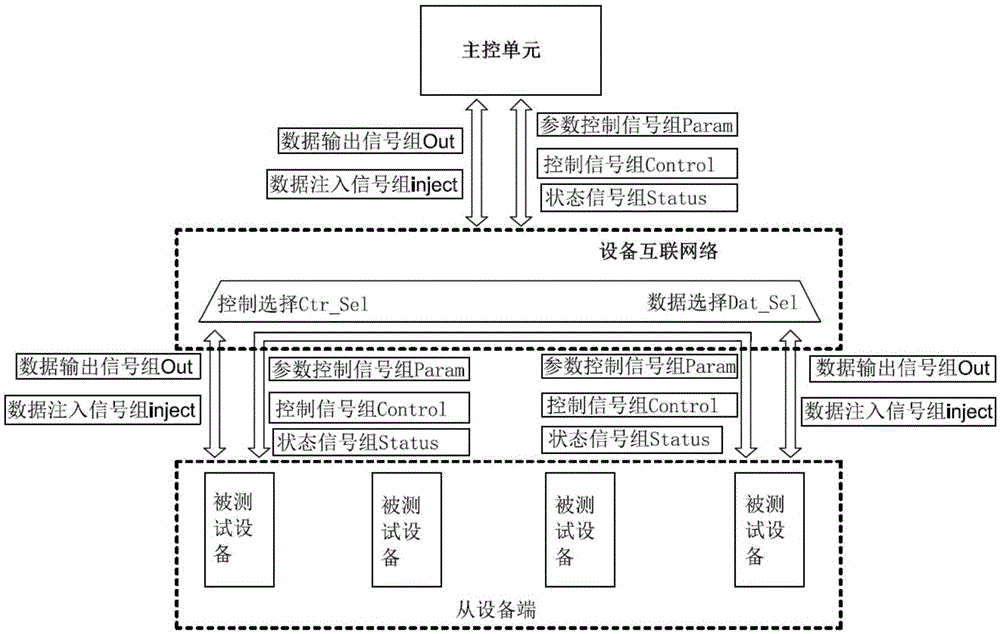

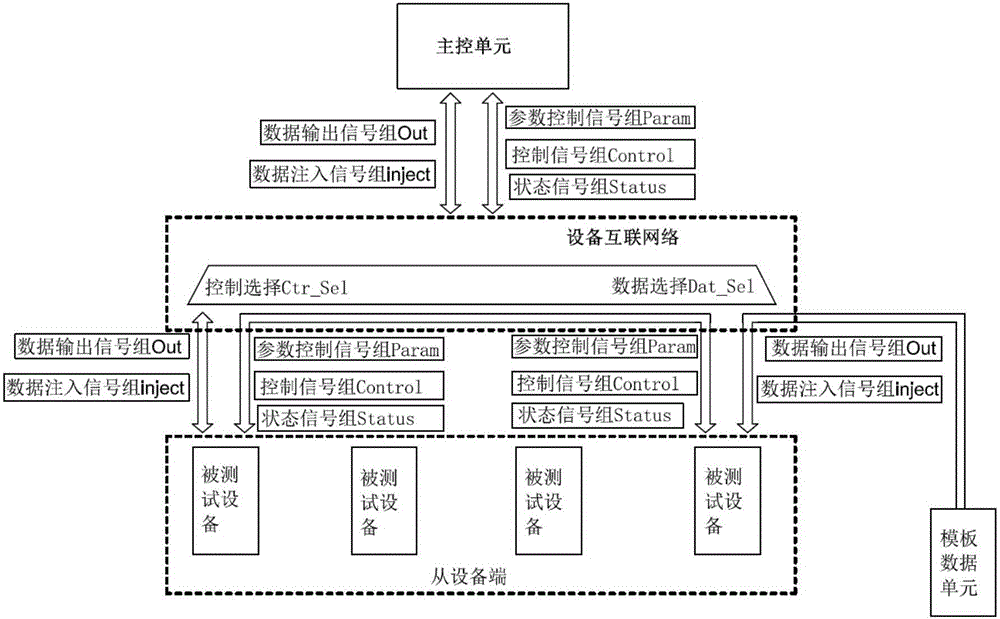

Method used

Image

Examples

Embodiment 1

[0093] A typical embedded system includes FPGA chip, DSP chip and various peripheral interface chips. FPGA and DSP are connected by external bus EMIF. FPGA has external SRIO interface, UART bus interface, SPI bus interface and LVDS interconnection line. Using the traditional method to test the external interface of FPGA, it is necessary to write SRIO test program, LVDS test program, UART test program and SPI test program respectively. Various test programs may be individual test programs, or they may be integrated into one test program. However, each module of DSP operation does not have a unified underlying driver interface, and the driver is customized for each module, which is highly dependent on the platform. If the DSP is replaced by PPC, in addition to the modification of the driver program, the test module in the FPGA will also be modified accordingly, and the test process and result display will also have some changes.

[0094] Use the Tbus bus standard to design each ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More