Scan chain re-sequencing method

A scanning chain and rerouting technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of wiring congestion, large area and power consumption overhead, layout and wiring congestion, etc., to reduce area and alleviate Effects of Routing Congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to enable those skilled in the art to better understand the solutions of the present invention, the following will clearly and completely describe the technical solutions in the embodiments of the present invention in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments are only It is an embodiment of a part of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts shall fall within the protection scope of the present invention.

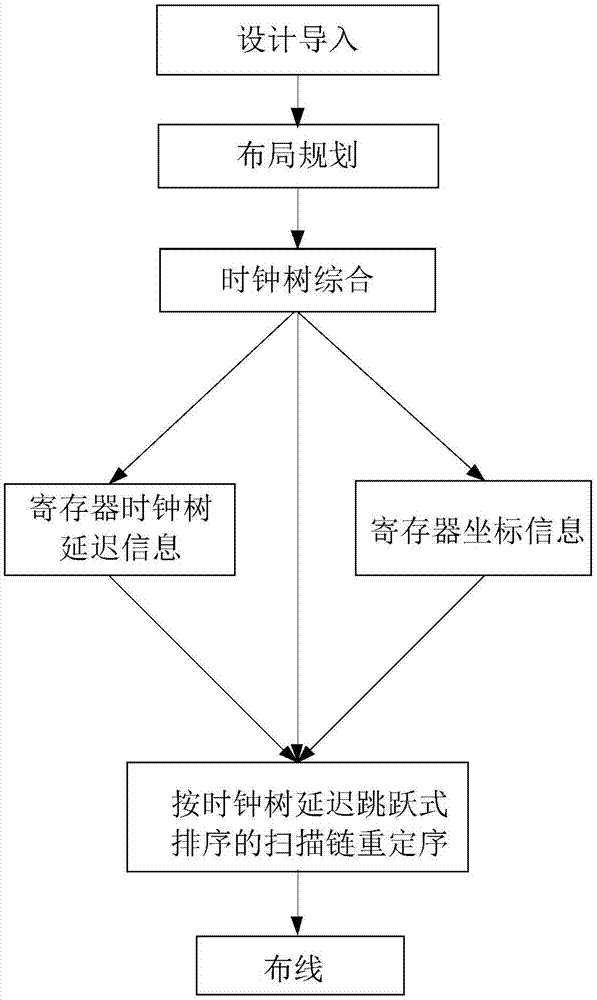

[0021] The scan chain reordering method proposed in the embodiment of the present invention is a method of sorting according to clock tree delay and jumping, which is implemented after designing clock tree synthesis. Refer to figure 1 Shown is the physical design process of the present invention, the main idea of the present inven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More