Multiple grid electrode neuron transistor, manufacturing method therefor and formed nerve network

A technology of transistors and neurons, which is applied in the field of multi-gate neuron transistors and their preparation methods and neural networks, can solve the problems of high power consumption, low power consumption that does not meet the requirements of the human brain, and cumbersome preparation processes, and achieve space The effect of high utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

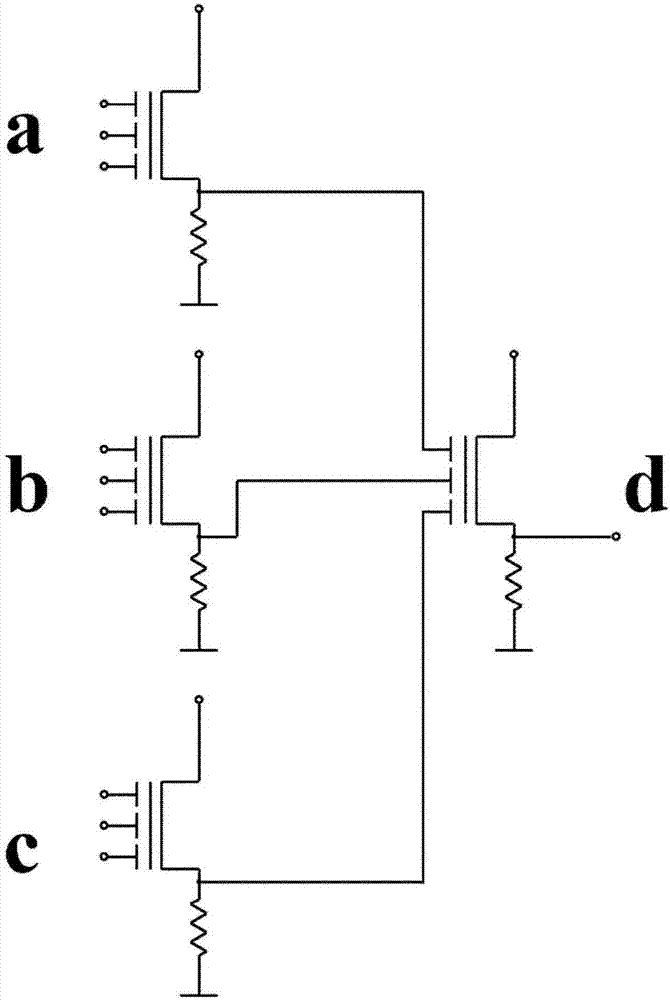

[0028] The technical solutions of the present invention will be described in detail below with reference to the accompanying drawings.

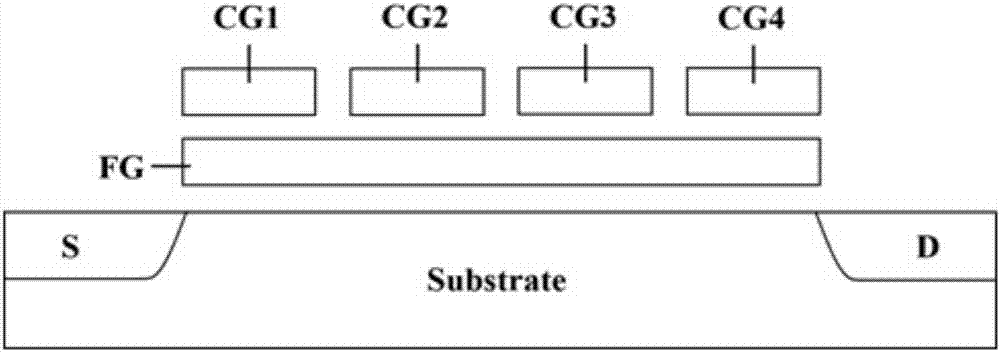

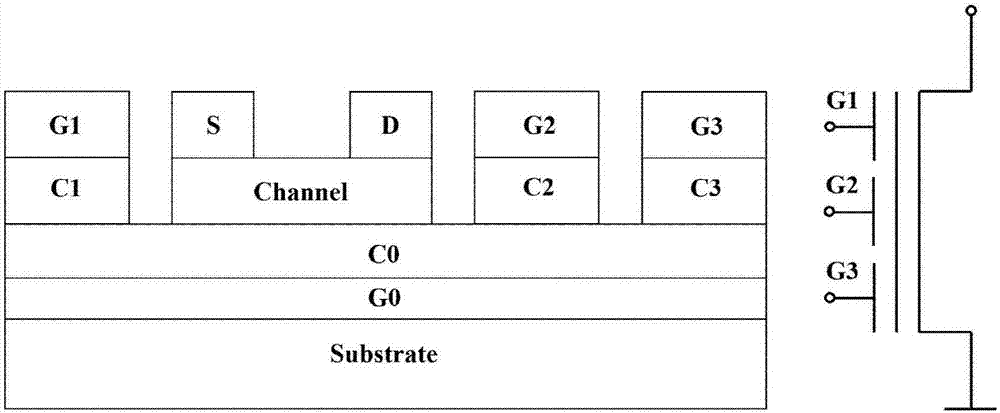

[0029] like figure 2 As shown, a multi-gate neuron transistor includes a substrate Substrate, a floating gate electrode G0, a gate dielectric layer C0, a source electrode S, a drain electrode D, a channel layer Channel, at least three groups of capacitor memory layers C1-C3 and There are at least three groups of input gates G1-G3 corresponding thereto. The floating gate electrode is set on the substrate, the gate dielectric layer is set on the floating gate electrode, the channel layer is set on the gate dielectric layer, and the source electrode and the drain electrode are respectively set on the channel layer. Both ends; each group of capacitance memory layers and input gates are not in contact with the channel layer; in each group of capacitance memory layers and input gates, the capacitance memory layer is located on the gate dielectric...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More