Chip verification method, device and system

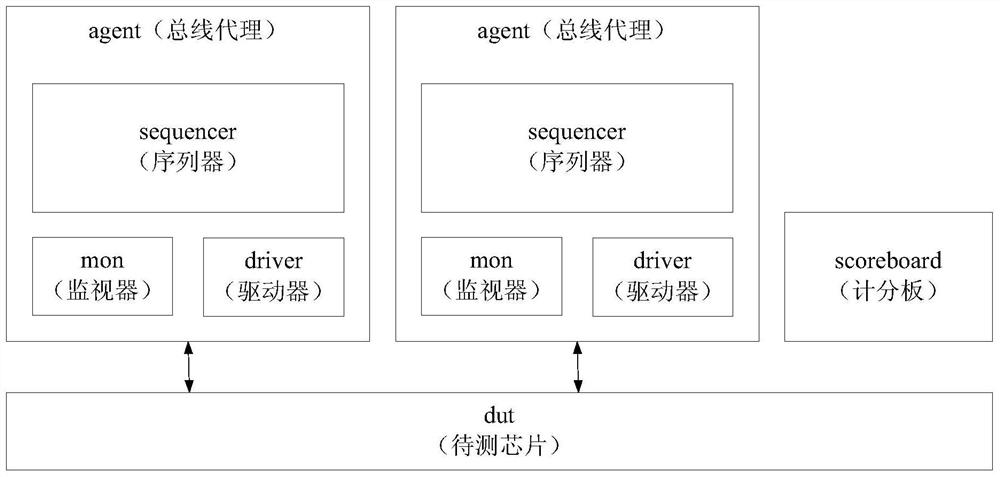

A chip and verification platform technology, applied in the communication field, can solve the problems of lack of hierarchy in the verification architecture and low platform reusability, and achieve the effect of improving reusability and verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Hereinafter, the present invention will be described in detail with reference to the drawings and examples. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

[0031] It should be noted that the terms "first" and "second" in the description and claims of the present invention and the above drawings are used to distinguish similar objects, but not necessarily used to describe a specific sequence or sequence.

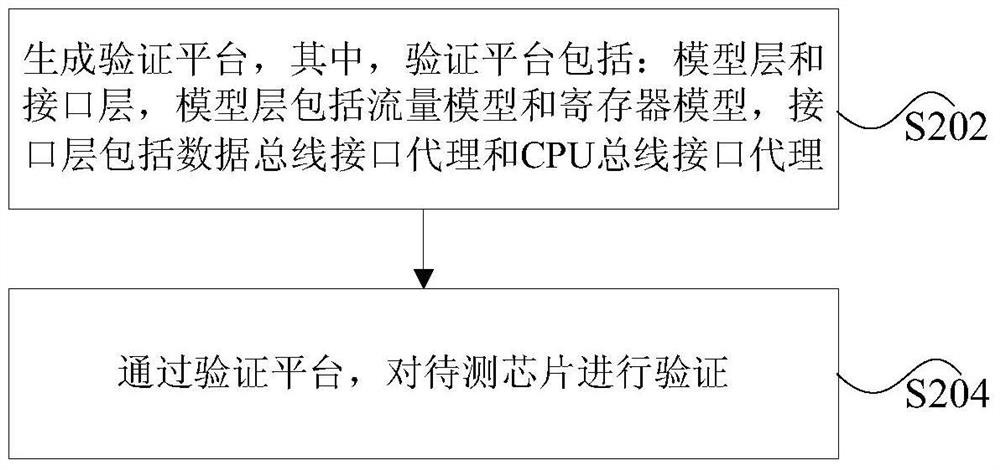

[0032] In this embodiment, a chip verification method is provided, figure 2 is a flowchart of a chip verification method according to an embodiment of the present invention, such as figure 2 As shown, the process includes the following steps:

[0033] Step S202, generating a verification platform, wherein the verification platform includes: a model layer and an interface layer, the model layer includes a traffic model and a register model, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More