Clock signal source with low phase noise and adjustable duty cycle

A clock signal and duty cycle technology, applied in the direction of automatic power control, instrumentation, electrical digital data processing, etc., can solve the problem that the phase noise of the output clock does not meet the requirements, so as to reduce the production test cost, improve the test efficiency, Optimizing the effect of the test setup

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings; it should be understood that the preferred embodiments are only for illustrating the present invention, rather than limiting the protection scope of the present invention.

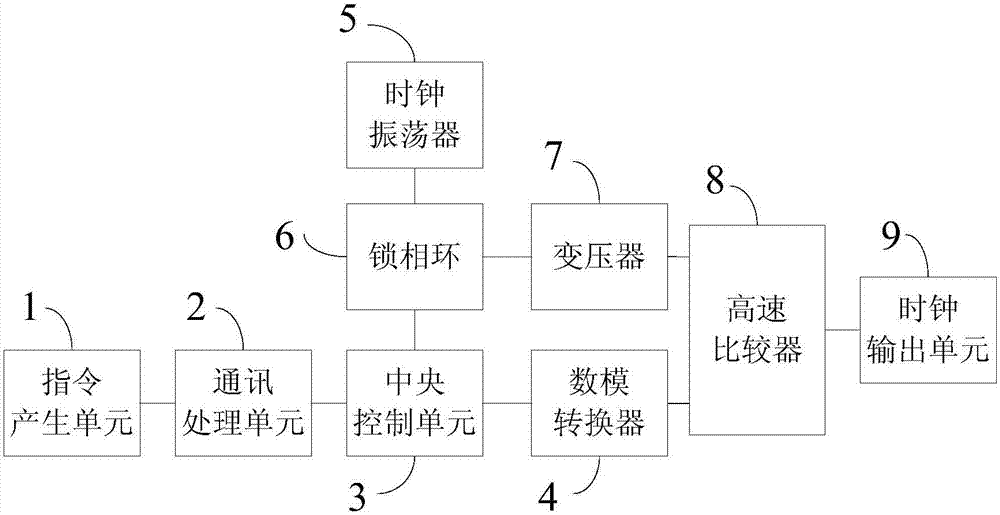

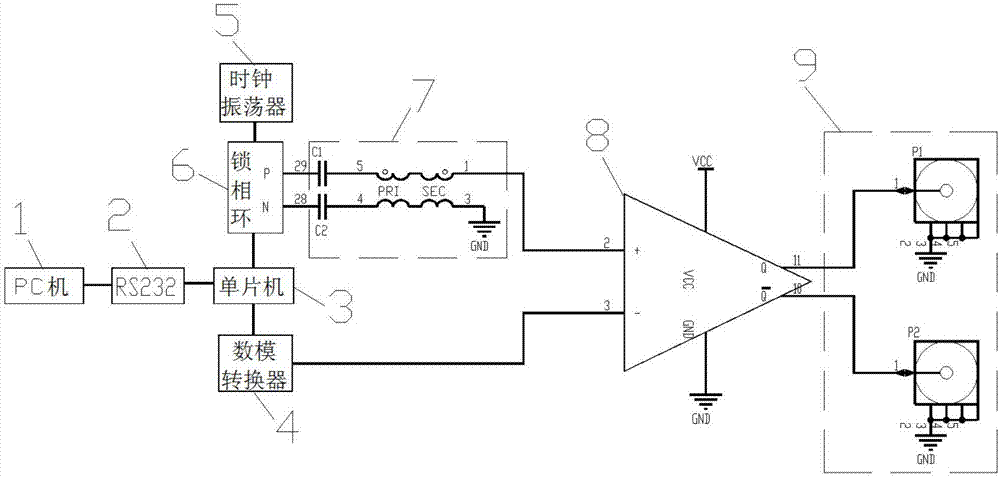

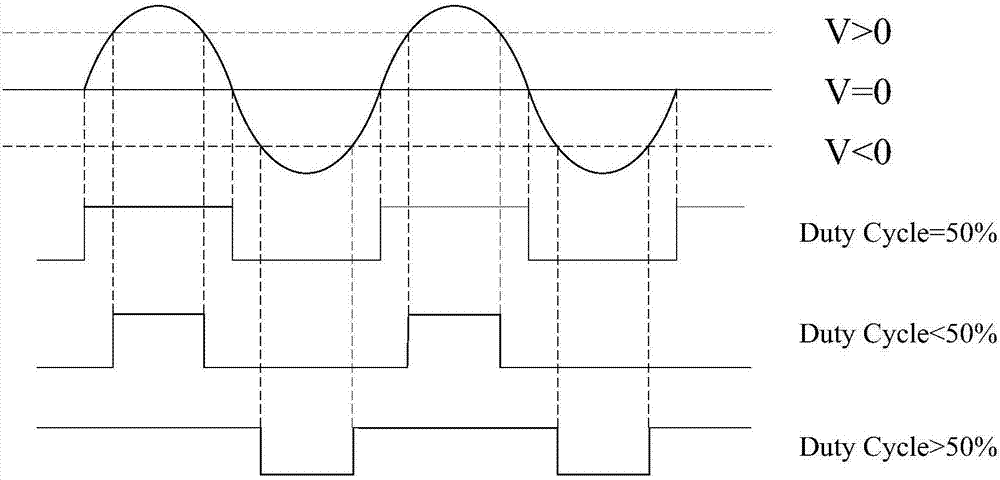

[0029] Please refer to figure 1 As shown, the present invention provides a clock signal source with low phase noise and adjustable duty ratio, including an instruction generation unit 1, a communication processing unit 2, a central control unit 3, a digital-to-analog converter 4, a clock oscillator 5, and a phase-locked loop 6. Transformer 7, high-speed comparator 8 and clock output unit 9; wherein,

[0030] Instruction generation unit 1: used to generate control signal instructions for controlling the duty cycle and frequency of the output clock;

[0031] The communication processing unit 2: receives the control signal command from the command generation unit 1, and e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More