Direct solution technology-based VLSI standard unit layout method

A standard cell, layout method technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as inability to guarantee layout quality, density constraint error, and solution quality impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

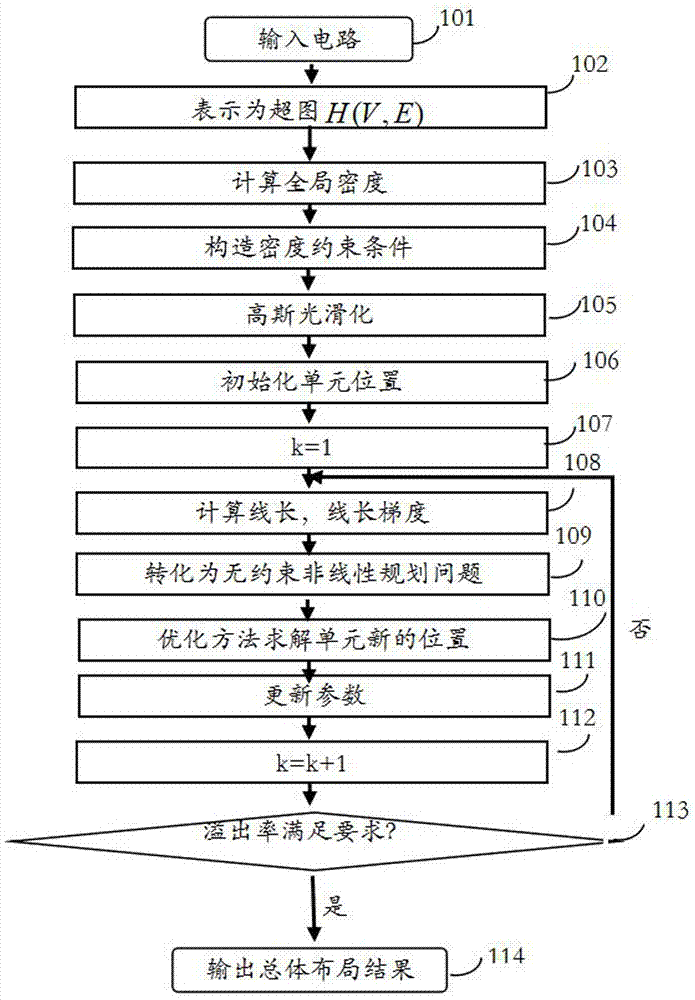

[0075] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings.

[0076] The present invention provides a VLSI standard cell layout method based on direct solution technology, which is realized according to the following steps:

[0077] Step (1) represents the circuit as a hypergraph H={V,E};

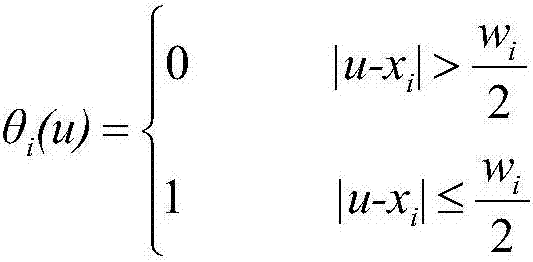

[0078] Step (2) calculates the global density function;

[0079] Step (3) using the global density function to construct density constraints;

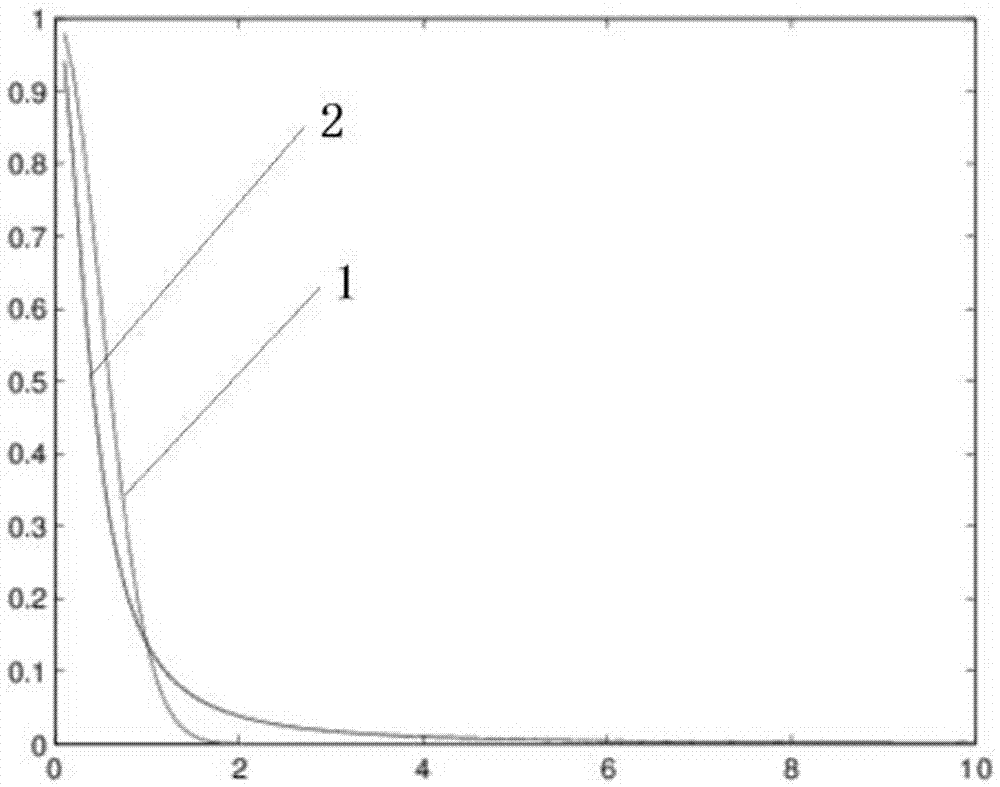

[0080] Step (4) uses a modified Gaussian function to perform convolution smoothing;

[0081] Step (5) initializes the position of the unit with an unconstrained quadratic programming method;

[0082] Step (6) k=1;

[0083] Step (7) calculates line length, line length gradient;

[0084] Step (8) adopts the penalty function method to convert the line length target and the density constraint of the VLSI global layout into an unconstrained nonlinear programming problem; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More