Low temperature polysilicon thin film transistor and its manufacturing method

A technology of thin-film transistors and low-temperature polysilicon, which is applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as grain boundary defects, and achieve the effect of eliminating compatibility and grain boundary defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

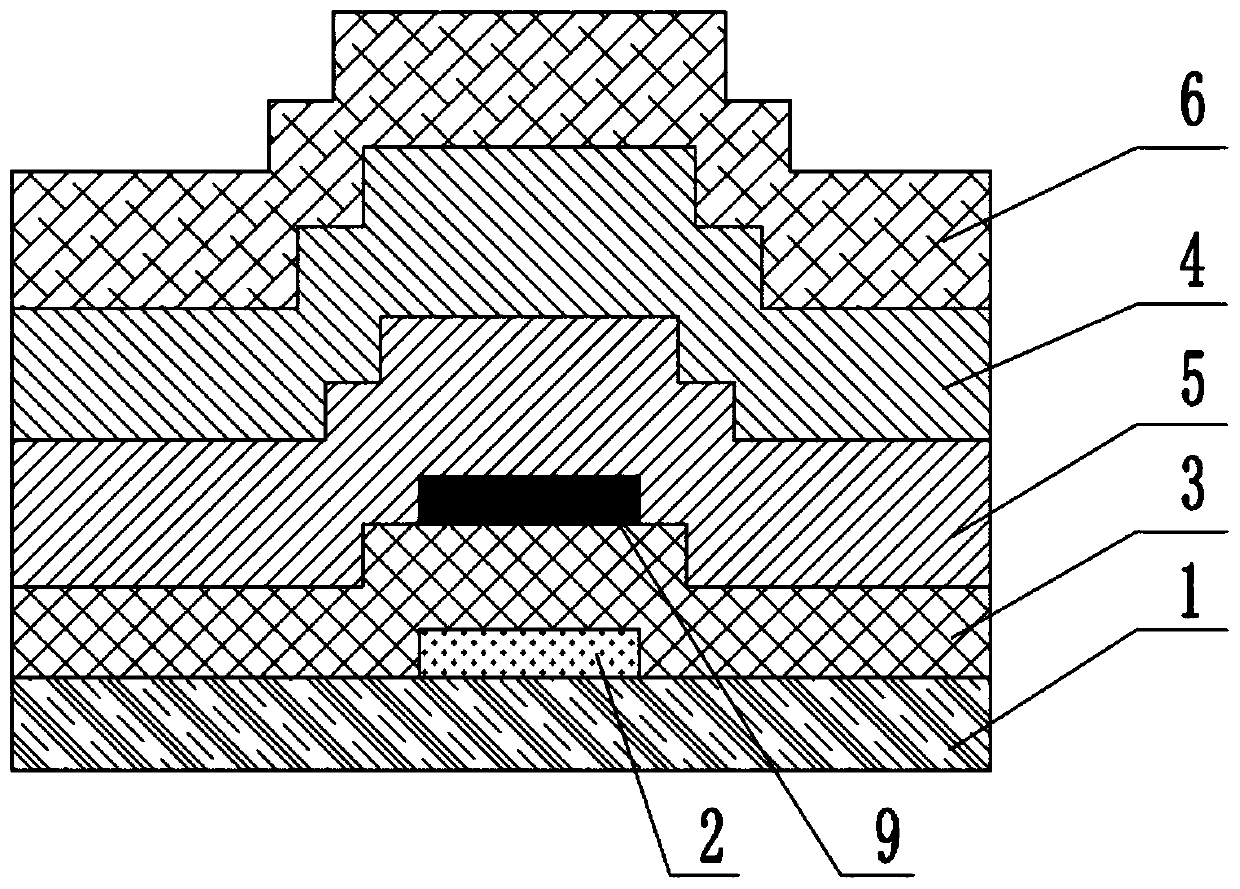

[0034] Such as image 3 As shown, an embodiment of the present invention provides a method for manufacturing a low-temperature polysilicon thin film transistor, which includes the following steps:

[0035] The first step: forming a polysilicon thin film layer 2 on the substrate 1, patterning the polysilicon thin film layer 2 to obtain an active layer, and forming a gate insulating layer 3 on the active layer.

[0036] Step 2: forming a silicon oxide dielectric layer 4 on the gate insulating layer 3 .

[0037] Wherein, the thickness of the silicon oxide dielectric layer 4 can be adjusted as required, for example In this embodiment, the thickness of the silicon oxide dielectric layer 4 is It is to achieve standardized production and facilitate subsequent operations.

[0038] Step 3: forming a silicon nitride dielectric layer 5 on the silicon oxide dielectric layer 4 .

[0039] While forming the silicon nitride dielectric layer 5 , hydrogen gas is added for hydrogenation tr...

Embodiment 2

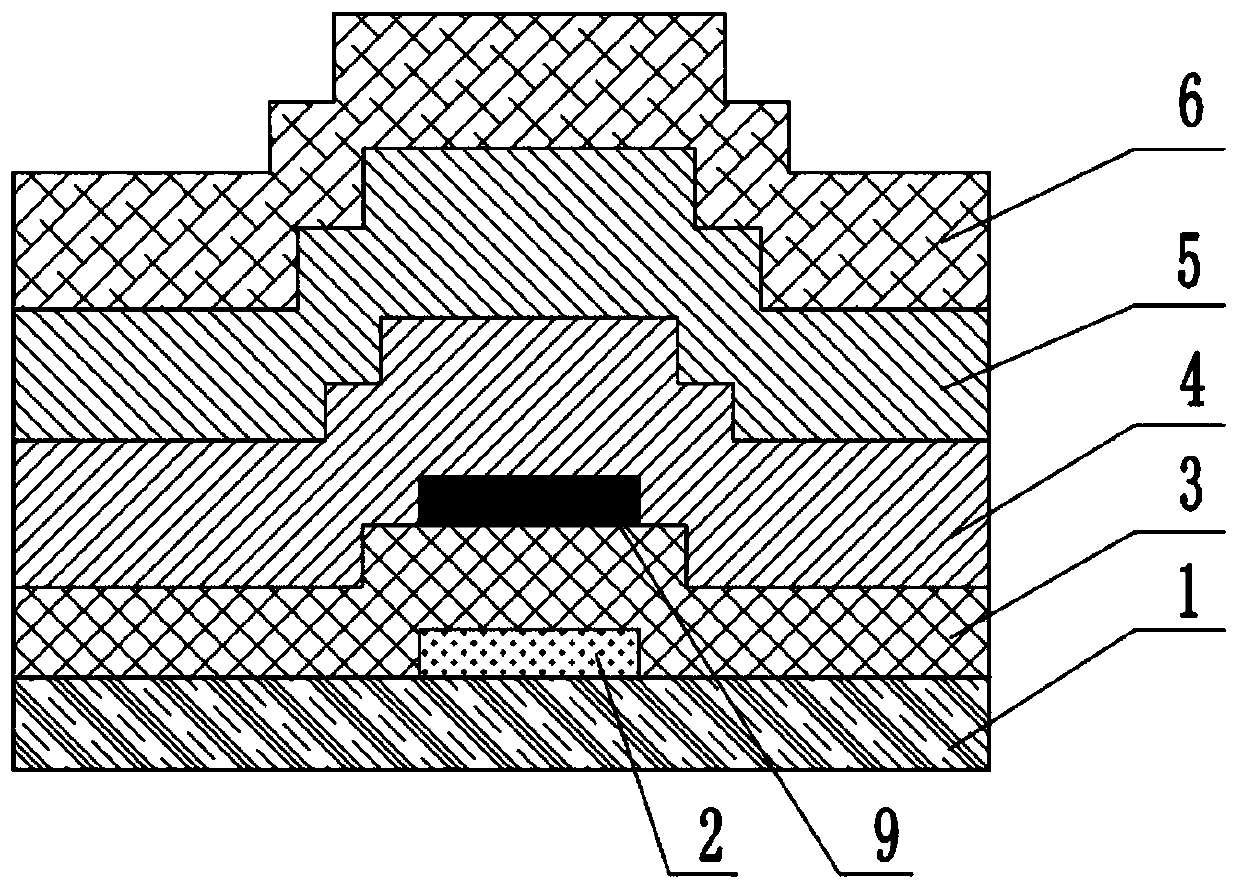

[0044] Such as Figure 4 As shown, an embodiment of the present invention provides a method for manufacturing a low-temperature polysilicon thin film transistor, which includes the following steps:

[0045] The first step: forming a polysilicon thin film layer 2 on the substrate 1, patterning the polysilicon thin film layer 2 to obtain an active layer, and forming a gate insulating layer 3 on the active layer.

[0046] Step 2: depositing a first silicon nitride layer 7 on the gate insulating layer 3 , and then depositing a silicon oxide dielectric layer 4 .

[0047] Wherein, the thickness of the first silicon nitride layer 7 is E.g

[0048] The advantage of depositing the first silicon nitride layer 7 before forming the silicon oxide dielectric layer 4 is: because the etching atmosphere of silicon nitride and silicon oxide is different, generally after the etching of the silicon nitride dielectric layer 5 is completed, start again. Etching the silicon oxide dielectric la...

Embodiment 3

[0057] Such as Figure 5 As shown, an embodiment of the present invention provides a method for manufacturing a low-temperature polysilicon thin film transistor, which includes the following steps:

[0058] The first step: forming a polysilicon thin film layer 2 on the substrate 1, patterning the polysilicon thin film layer 2 to obtain an active layer, and forming a gate insulating layer 3 on the active layer.

[0059] Step 2: first hydrogenate the gate insulating layer 3 by using hydrogen plasma, and then deposit and form a silicon oxide dielectric layer 4 .

[0060] Wherein, the time for the hydrogenation treatment is 10-40s, preferably 30s; the second silicon nitride layer 8 is formed after the hydrogenation treatment, and the thickness of the second silicon nitride layer 8 is E.g

[0061] Depositing the second silicon nitride layer 8 first can facilitate precise control of the time when the silicon oxide of the gate insulating layer 3 starts to be etched during dry et...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More