Sealing ring with esd protection

A technology of ESD protection and sealing ring, which is applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., and can solve problems such as not having ESD protection function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

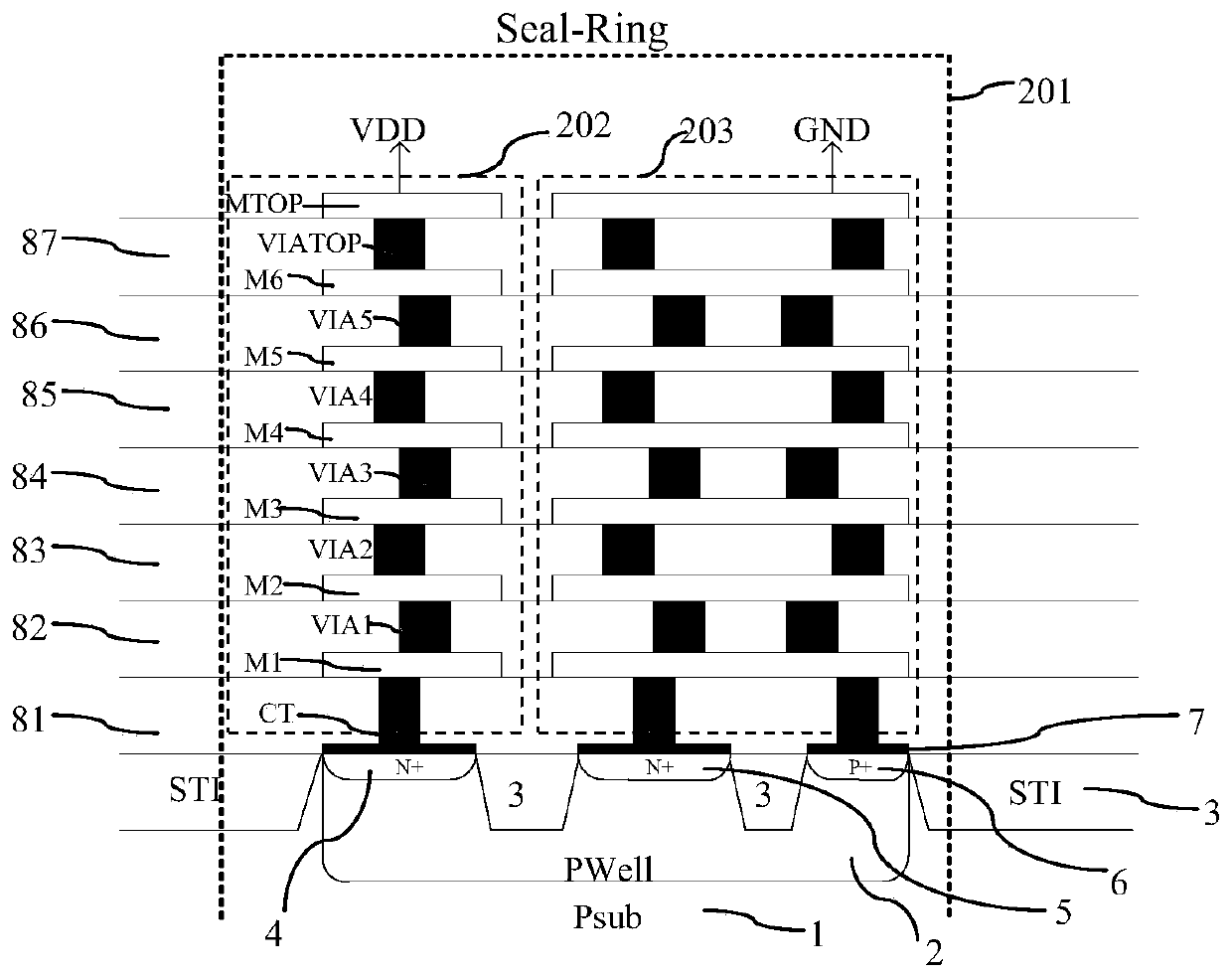

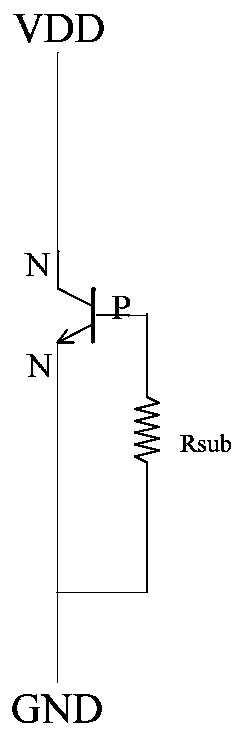

[0035] Such as Figure 2A Shown is a schematic diagram of a sealing ring with an ESD protection function according to the first embodiment of the present invention; Figure 2B yes Figure 2A The shown equivalent circuit diagram; the sealing ring with ESD protection function according to the first embodiment of the present invention includes: a substrate part structure formed in the semiconductor substrate 1 and a metal connection structure forming the top surface of the semiconductor substrate 1 . Figure 2A The middle semiconductor substrate 1 is a P-type semiconductor substrate, namely Psub. Preferably, the semiconductor substrate 1 is a silicon substrate.

[0036] A sealing ring with a stress protection function is formed by superposition of the substrate partial structure and the metal connection structure. Figure 2A The area of the middle sealing ring is the area framed by the dotted box 201 .

[0037] The partial structure of the substrate includes:

[0038]The f...

no. 2 example

[0048] Such as Figure 3A Shown is a schematic diagram of a sealing ring with ESD protection function according to the second embodiment of the present invention; Figure 3B yes Figure 3A The shown equivalent circuit diagram; the difference between the second embodiment of the present invention and the first embodiment of the present invention is that in the second embodiment of the present invention:

[0049] The first conductivity type is N type, the second conductivity type is P type, and the bipolar transistor is a PNP transistor.

[0050] Figure 3A In , the area of the sealing ring is the area framed by the dotted box 201a.

[0051] Figure 3A , so the above-mentioned first conductivity type well region is marked with mark 2a alone, and the first conductivity type well region 2a is an N-type well region (NWell); the first doped region is marked with 4a alone, and the second The doped region is marked with 5a alone, and the third doped region is marked with 6a alo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More