clock recovery device

A technology of clock recovery and clock phase, which is applied in the field of communication, can solve problems such as complex circuit design and unfavorable hardware circuit implementation, and achieve the effect of simplifying complexity and facilitating implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0089] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

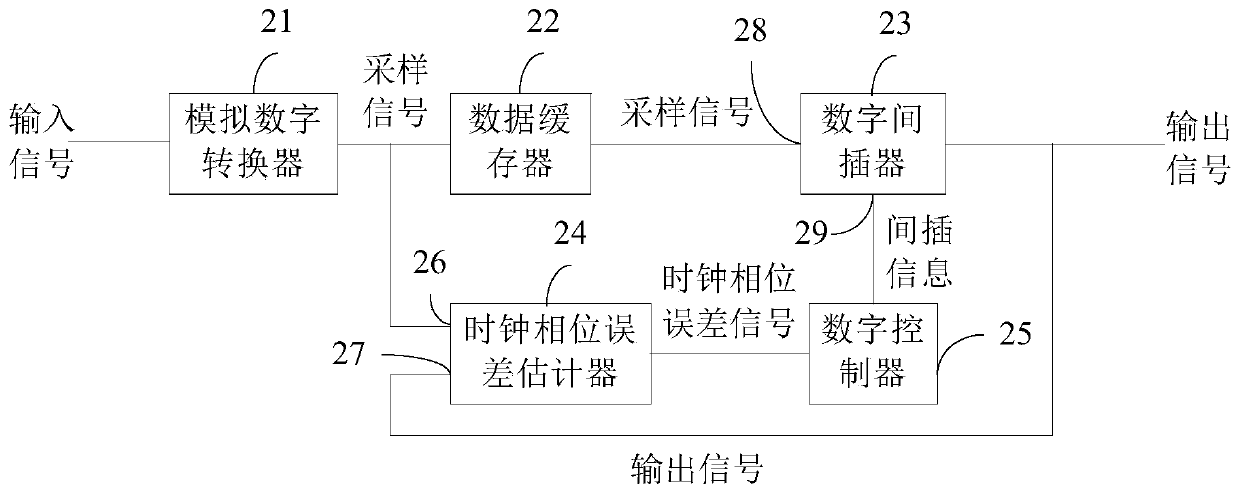

[0090] figure 2 It is a schematic structural diagram of a clock recovery device provided in Embodiment 1 of the present invention. Such as figure 2 As shown, the device includes an ADC 21 , a data buffer 22 , a digital interleaver 23 , a clock phase error estimator 24 and a digital controller 25 .

[0091] Wherein, the output end of ADC 21 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More