Power-attack-resistant SM4 algorithm hardware implementation system

A hardware implementation and anti-power consumption technology, applied in the field of information security, can solve the problem of power consumption generated by logic gates, and achieve the effect of defending against power consumption attacks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, and are not intended to limit the present invention.

[0017] The SM4 hardware circuit design in the prior art is not effective in defending against power consumption attacks.

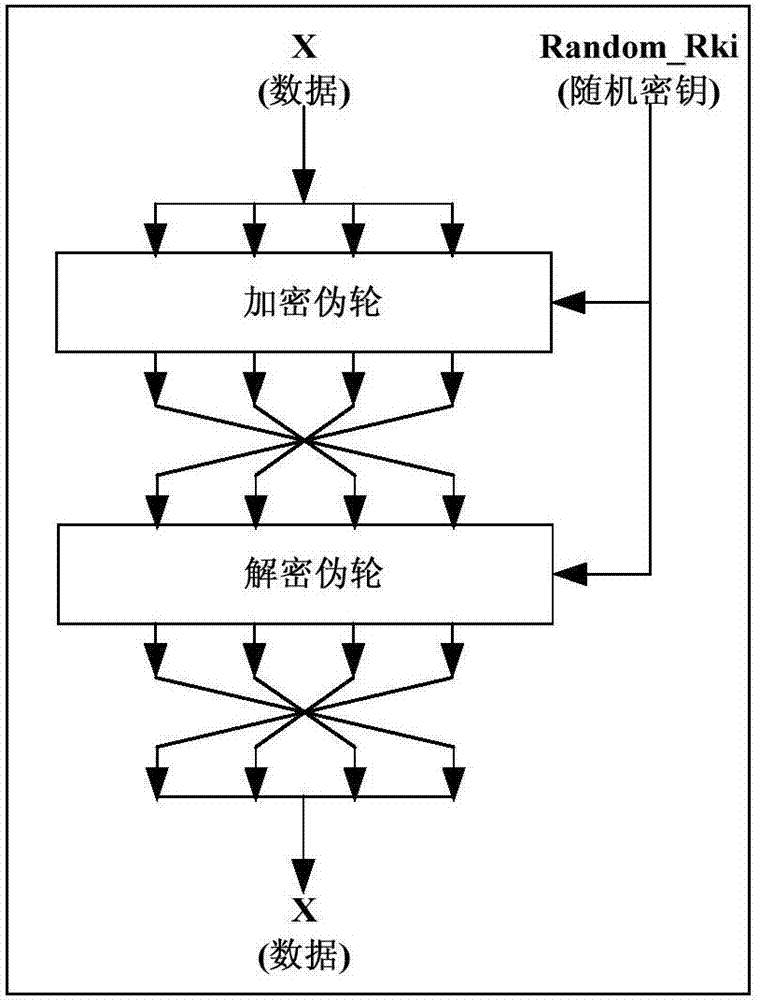

[0018] According to the characteristics of power consumption attack in the present invention, if the correlation between power consumption and data is destroyed, the power consumption attack method will not work. In the present invention, using the method of randomly inserting pseudo-round operation pairs, inserting pseudo-round operation pairs that have nothing to do with data operation into the SM4 hardware circuit of plaintext and key, and controlling the number of inserted...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More