Control method for reducing impact on LCL-type grid-connected inverter from digital control time delay

A technology of digital control and control method, which is applied to the output power conversion device, the conversion of AC power input to DC power output, electrical components, etc. The minimum phase attribute is difficult to guarantee and other problems, to achieve the effect of compensating for delay, improving compatibility and system stability margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

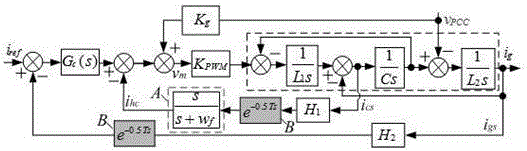

[0022] The invention provides a control method for reducing the influence of digital control delay on the LCL grid-connected inverter, which can eliminate the PWM loading delay and combine the influence of sampling zero-order hold delay on the LCL active damping impedance characteristics, A compensation link for compensating the delay in the resonant frequency section of the active damping inner ring is proposed to improve the mutual compatibility between the system control frequency and the resonant frequency of the LCL filter.

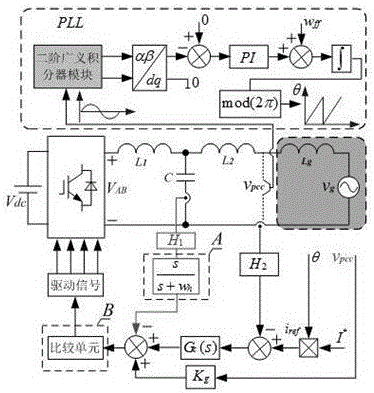

[0023] The structural diagram of the LCL type grid-connected inverter provided by the present invention is as follows figure 1 As shown: The LCL filter is composed of inverter side inductor L1, grid side inductor L2 and filter capacitor C. The phase-locked loop (PLL) module samples the common coupling point voltage Vp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More