Hybrid main storage architecture based efficient dynamic page scheduling method

A technology of dynamic page and scheduling method, applied in memory system, program startup/switching, resource allocation, etc., can solve problems such as low static power consumption, lack of scheduling strategy in application scenarios, and inability to further develop PCM read power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

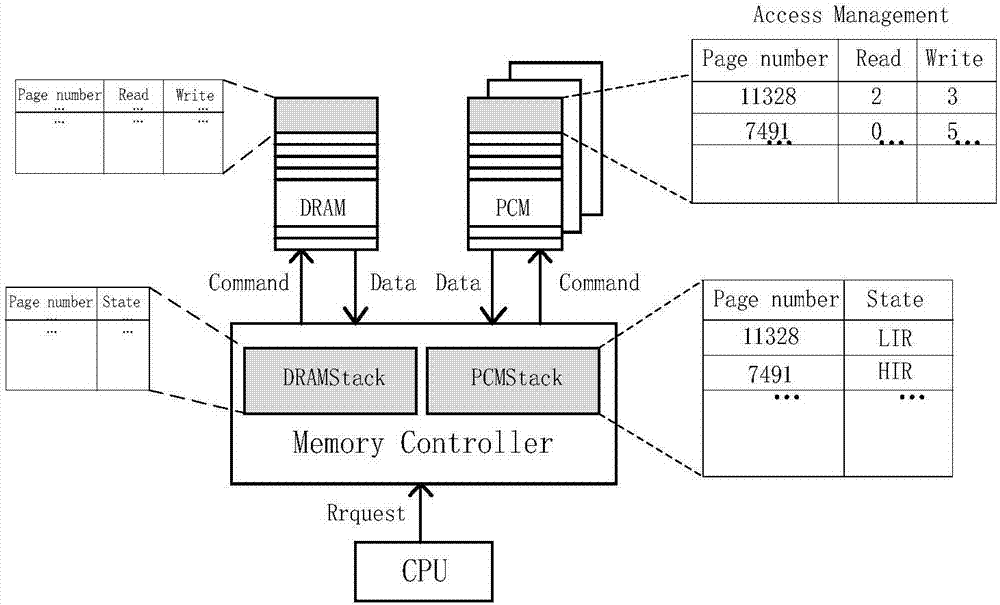

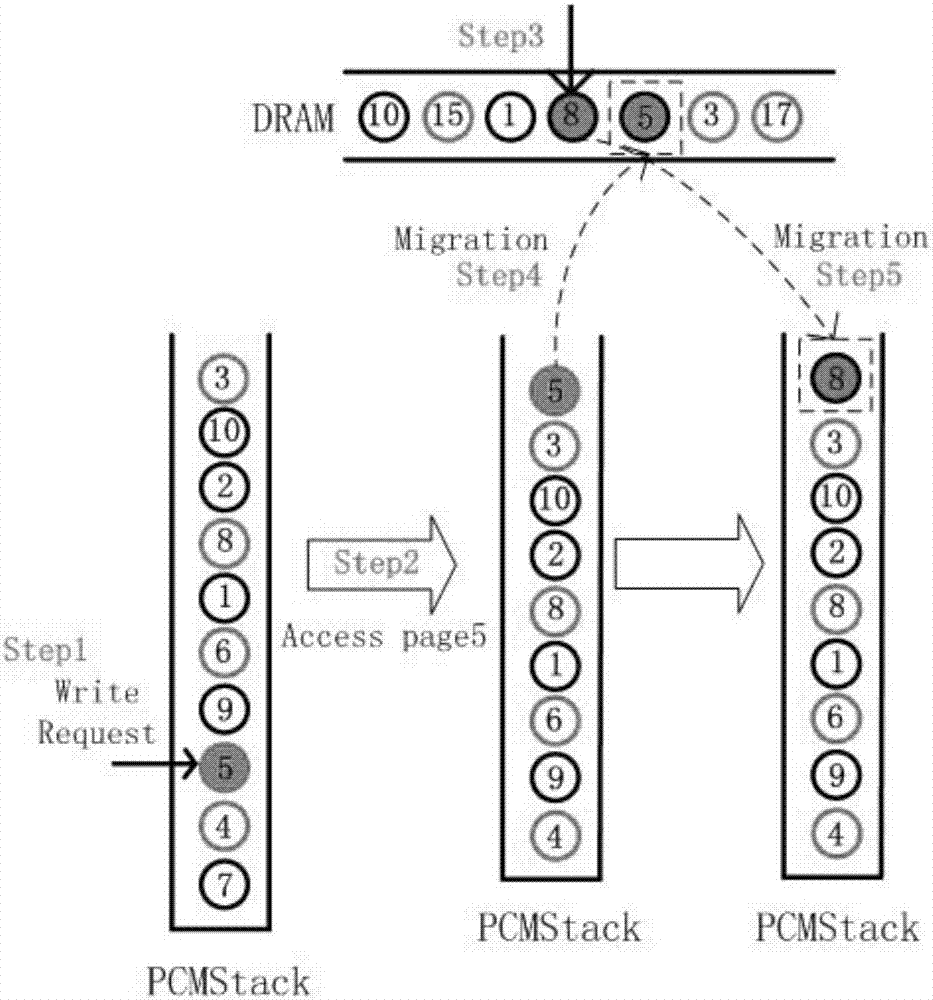

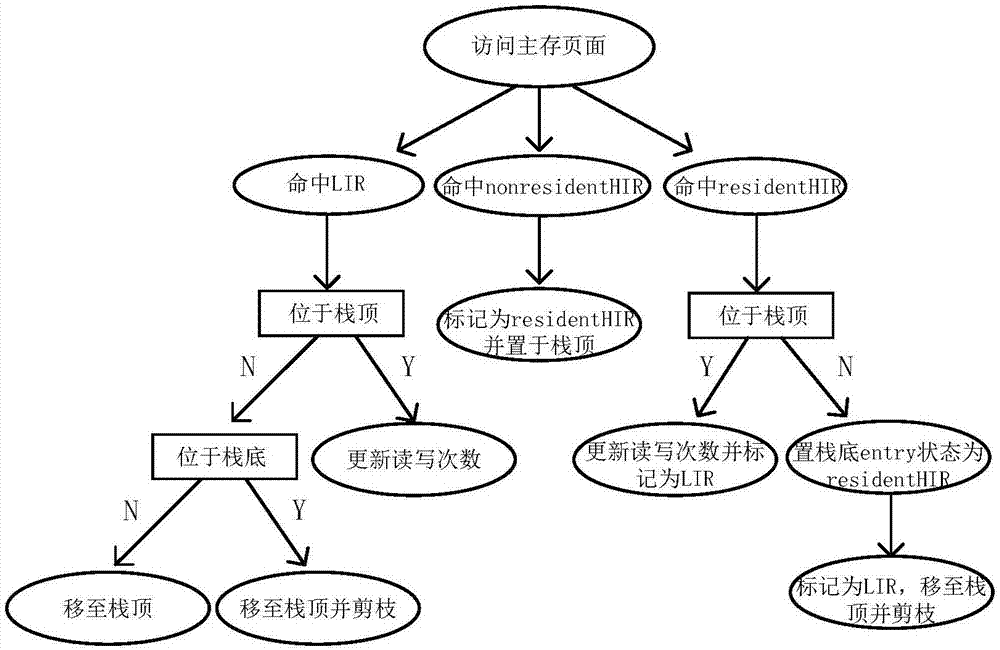

[0032] The LIRS (Low Inter Reference Recency Set) algorithm is an improved algorithm for the weak locality of LRU. It uses the concept of IRR (Inter-reference recency) to define the number of other pages visited during the last two visits of the same page. , while sorting pages with reference to recency, update the queue according to IRR, so as to accurately grasp the heat of data access in an application environment with weak locality. Wherein, each page corresponds to an entry, and each entry is a structure, that is, a data structure including information such as page address, reading and writing times, and status flags. The IRR of a cache block refers to the number of other non-repeated cache blocks accessed between successive accesses to this block. The non-repeated number of access to other blocks from the latest access to the current time of a block is called the recency of this block. The block is also the page in the present invention. It can be seen that in the stora...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More