Air-tight image chip packaging structure and manufacturing method thereof

A chip packaging structure and airtight technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, and electric solid-state devices, can solve problems such as low production efficiency, unfavorable image sensor thinning process, and weakened image chip strength.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

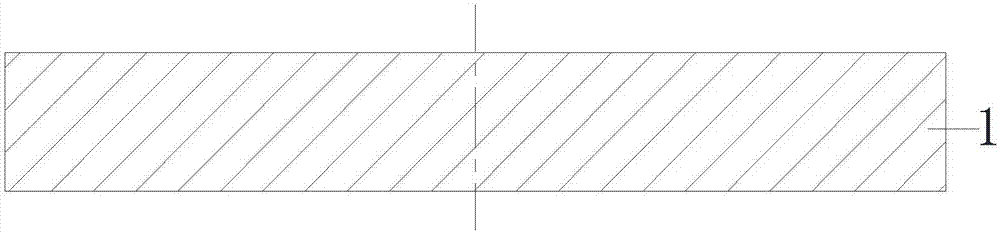

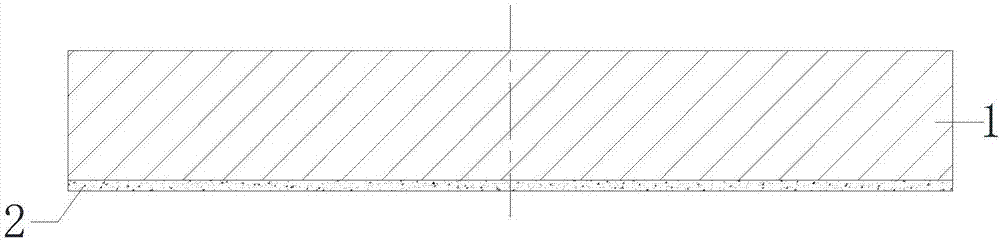

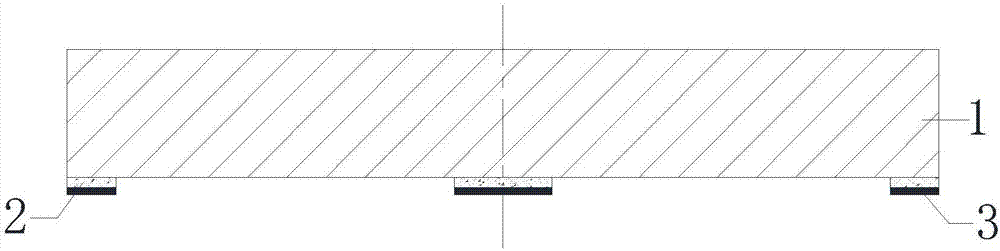

[0029] In order to make the present invention more obvious and understandable, the specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings. For convenience of description, the components in the structures in the drawings of the embodiments are not scaled according to the normal scale, so they do not represent the actual relative sizes of the structures in the embodiments.

[0030] Such as Figure 14 As shown, the packaging structure of an image chip disclosed in the present invention includes at least one image chip 700 and a cofferdam 4. The image chip 700 includes a functional surface and a non-functional surface opposite to it, and the functional surface includes solder pads 701 and Functional area 702, the front side of the cofferdam 4 includes a conductive circuit 3, the solder pad 701 on the functional surface of the image chip 700 is bonded and electrically connected to the conductive circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More