Offset calibration circuit for comparer in asynchronous successive approximation register analog-to-digital converter

An asynchronous successive approximation, analog-to-digital converter technology, applied in the direction of analog/digital conversion calibration/test, analog/digital conversion, code conversion, etc. large problems, to achieve the effect of small overhead, restraining influence, and improving the accuracy of adjustment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The technical solution of the present invention will be further introduced below in conjunction with the accompanying drawings and specific embodiments.

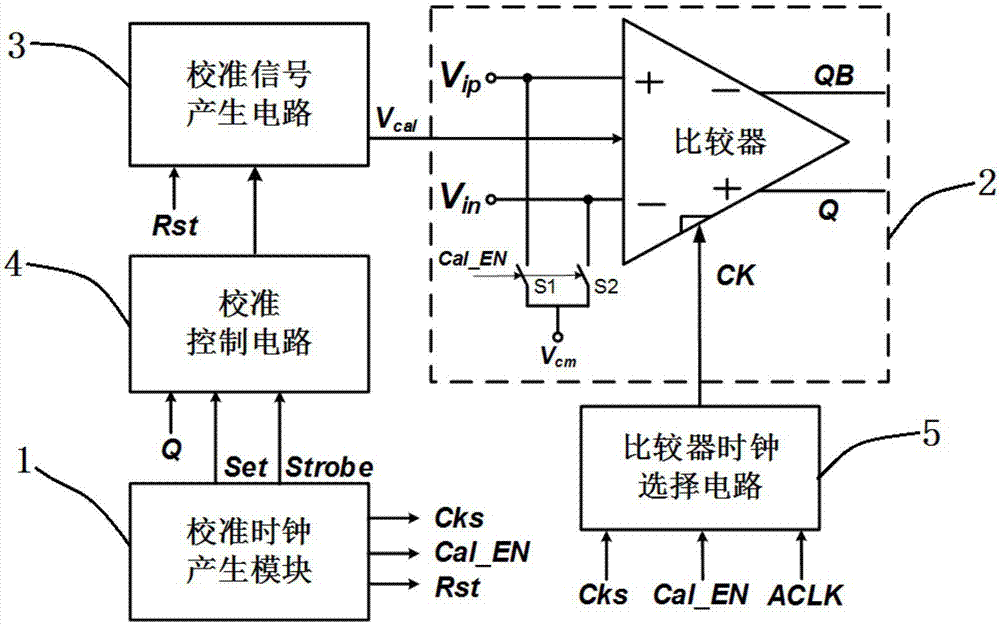

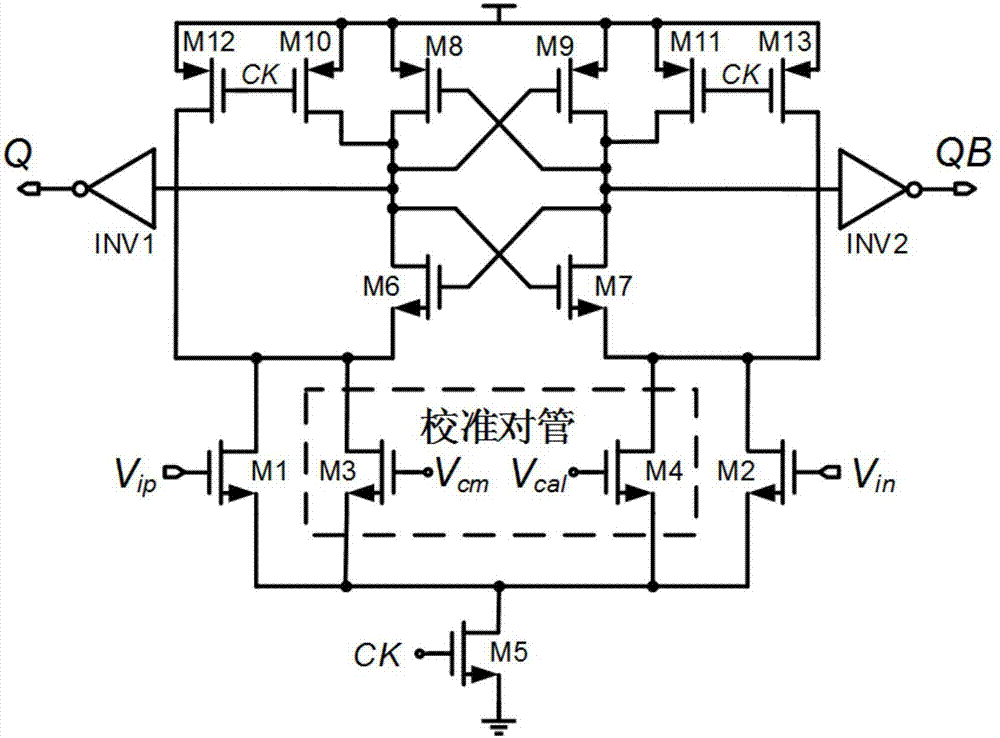

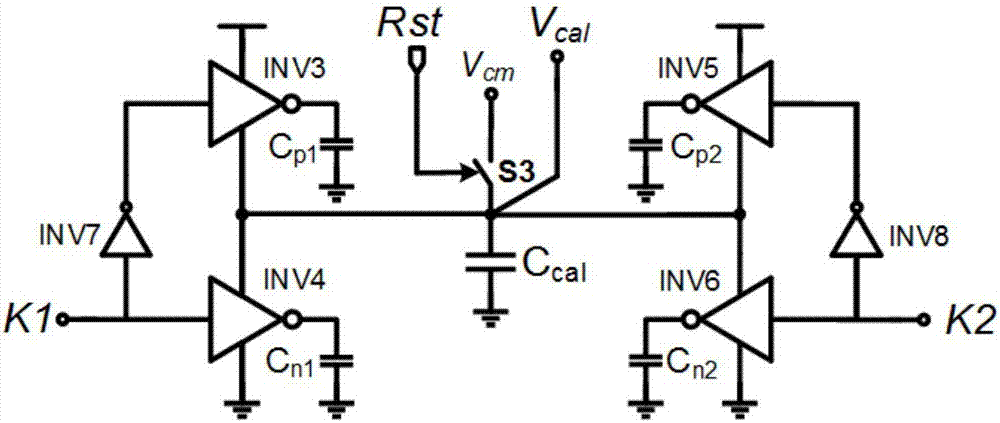

[0031] This specific embodiment discloses an offset calibration circuit of a comparator in an asynchronous successive approximation analog-to-digital converter, such as figure 1 As shown, it includes a calibration clock generation module 1, a basic dynamic comparator with a calibration pair tube 2, a calibration signal generation circuit 3, a calibration control circuit 4 and a comparator clock selection circuit 5; the calibration clock generation module 1 is used to generate and control dynamic comparison Global clock control signals for offset calibration of device 2, including SAR ADC sampling clock Cks, calibration enable signal Cal_EN, calibration start reset signal Rst, calibration set signal Set, and calibration strobe signal Strobe, the basic dynamic comparator with calibration pair 2 includes a basic single-s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More