Method for carrying out simulation verification on random access memory RAM and simulation verification system

A technology of random access memory and simulation verification, applied in the field of simulation verification system, can solve the problem of low efficiency of RAM simulation verification, and achieve the effect of saving workload and improving verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

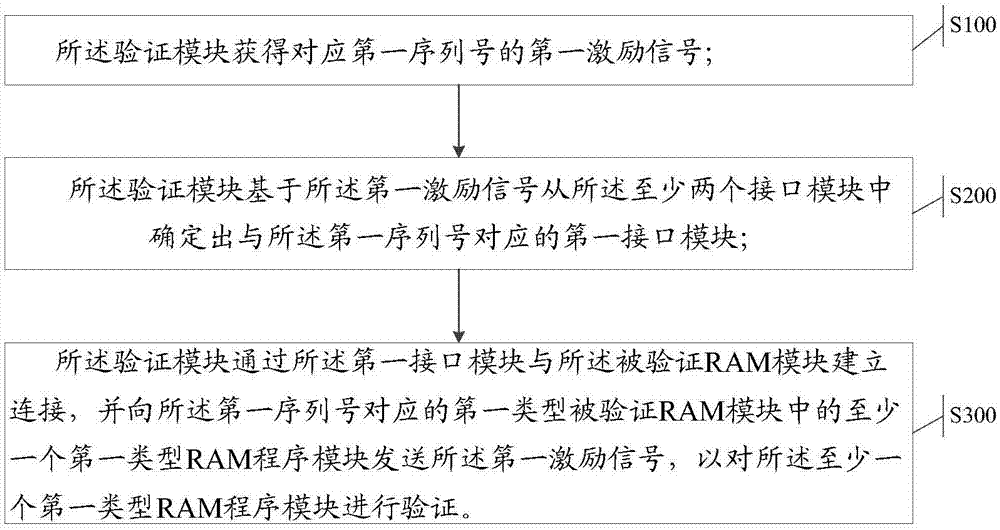

[0066] See figure 1 , in an embodiment of the present invention, a method for performing simulation verification on random access memory RAM is provided, which can be applied to a simulation verification system, wherein the process of the method can be described as follows:

[0067] S100: The verification module obtains a first excitation signal corresponding to a first serial number;

[0068] S200: The verification module determines a first interface module corresponding to the first serial number from the at least two interface modules based on the first excitation signal;

[0069] S300: The verification module establishes a connection with the verified RAM module through the first interface module, and sends at least one first type RAM program module in the first type of verified RAM module corresponding to the first serial number Sending the first excitation signal to verify the at least one first type RAM program module.

[0070] In S100, the first serial number may be ...

Embodiment 2

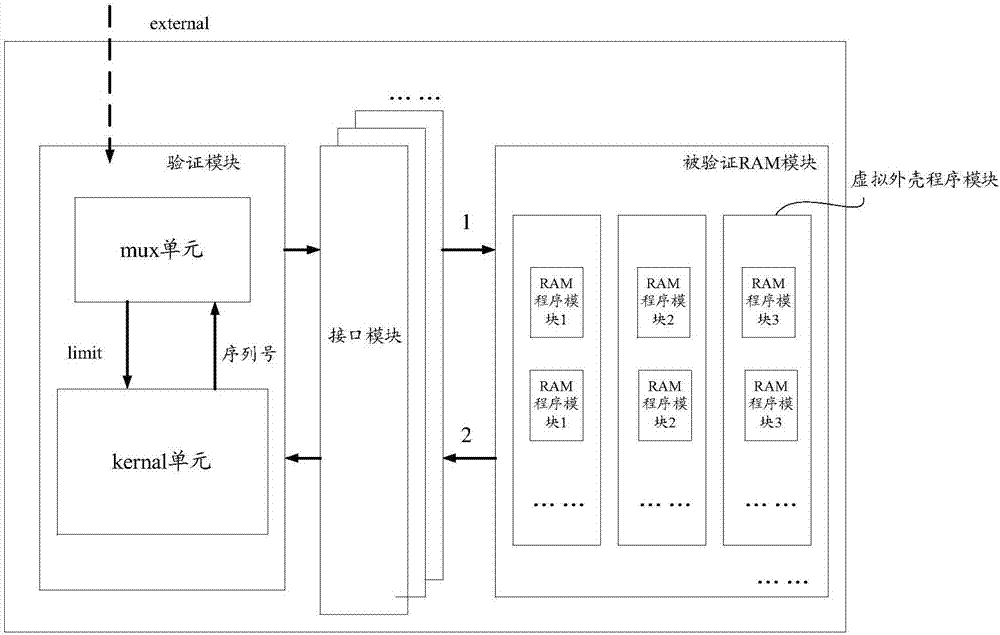

[0114] Based on the same inventive concept, see Figure 4 , the embodiment of the present invention also provides a simulation verification system, the simulation verification system includes a verification module 10 , a RAM module 20 to be verified and at least two interface modules 30 .

[0115] Wherein, the verification module 10 is configured to obtain a first excitation signal corresponding to the first serial number, and determine the first serial number corresponding to the first serial number from the at least two interface modules 30 based on the first excitation signal. An interface module, and establish a connection with the verified RAM module through the first interface module, and send at least one first type RAM program module in the first type of verified RAM module corresponding to the first serial number A first stimulus signal to verify the at least one first type RAM program module.

[0116] Optionally, the verification module 10 is used for:

[0117] rec...

Embodiment 3

[0134] In the embodiment of the present invention, a computer device is also provided, please refer to Figure 5 As shown, the computer device includes a processor 401, and the processor 401 is configured to implement the steps of the clock synchronization method provided by the embodiment of the present invention when executing the computer program stored in the memory 402.

[0135] Optionally, the processor 401 may specifically be a central processing unit, an application specific integrated circuit (Application Specific Integrated Circuit, ASIC), may be one or more integrated circuits for controlling program execution, and may use a field programmable gate array ( The hardware circuit developed by Field Programmable Gate Array (FPGA) can be a baseband processor.

[0136] Optionally, the processor 401 may include at least one processing core.

[0137] Optionally, the electronic device further includes a memory 402, and the memory 402 may include a read only memory (Read Onl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com