Power semiconductor chip and photomask and exposure method of chip

A power semiconductor and lithography technology, applied in the field of power electronics, can solve the problems of inability to apply complex structure chips, increasing the number of lithography plates, and not considering key dimensions, etc., to achieve the effect of simple graphics, reducing the number of use, and improving errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

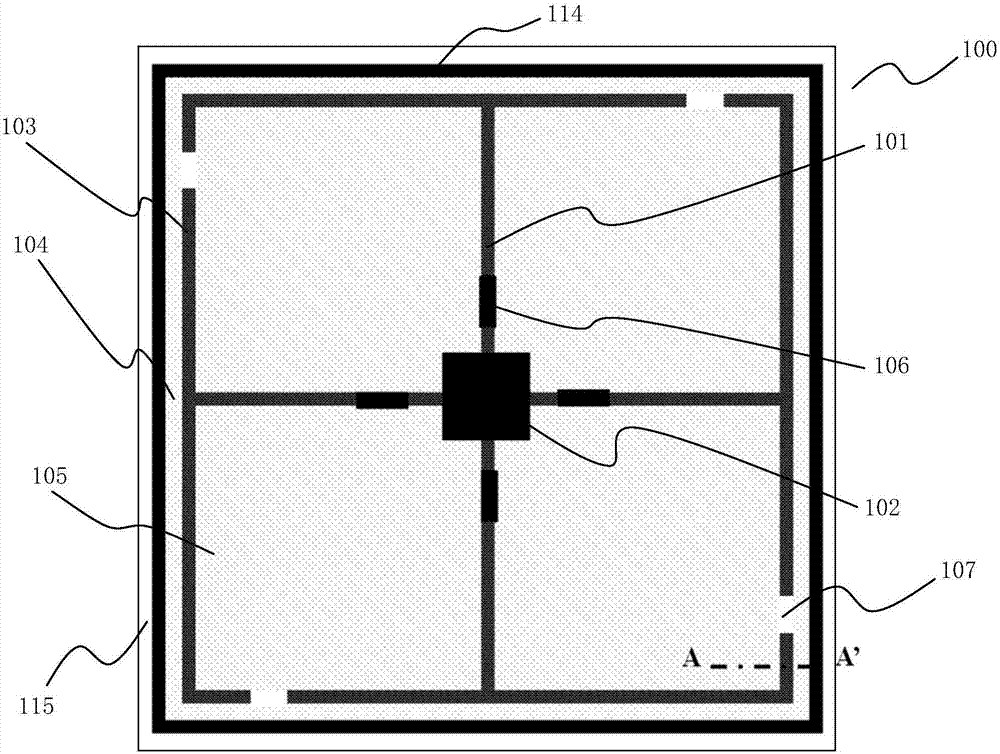

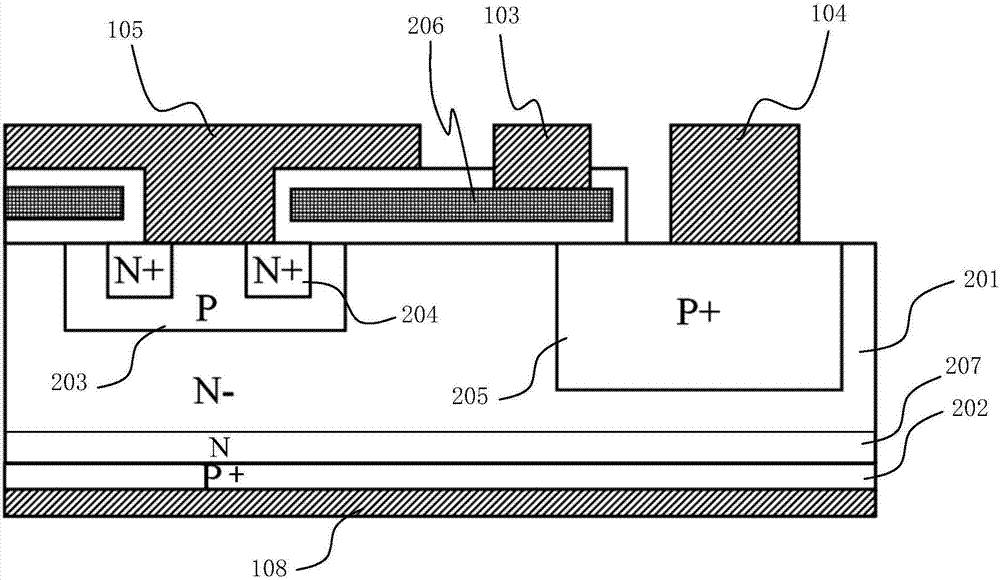

[0062] as attached figure 1 As shown, a specific embodiment of a power semiconductor chip includes: a termination region 114 , and an emitter region and a gate region located in the termination region 114 . The emitter region includes a peripheral emitter region 104 and a plurality of main emitter regions 105 , and the gate region includes a gate bar 101 , a main gate region 102 , a peripheral gate 103 and a gate resistor 106 . The peripheral gate 103 is located on the periphery of the main gate region 102 , and the peripheral gate 103 is discontinuous. The main gate region 102 is located in the center of the area surrounded by the peripheral gate 103 , and the peripheral gate 103 is connected to the main gate region 102 through a gate bar 101 , and a gate resistor 106 is arranged on the gate bar 101 . The shape of the main gate region 102 may be a centrosymmetric figure such as a circle, a square, or a regular polygon. The peripheral grid 103 includes disconnection points 1...

Embodiment 2

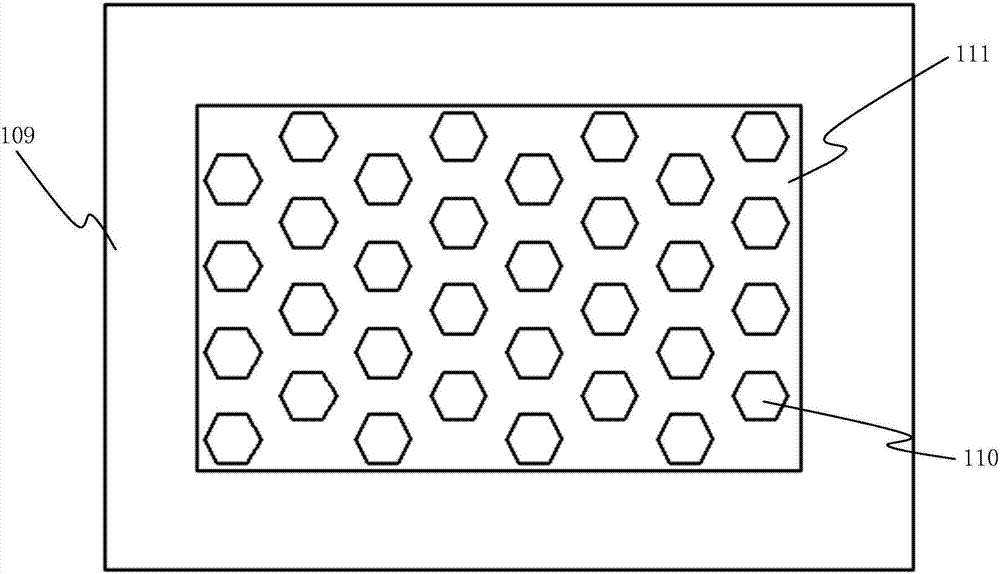

[0066] as attached Figure 4 As shown, on the basis of Embodiment 1, the emitter region and the gate region on the front of the chip 100 are further formed with a first metallization layer 109 through a metallization process, and a dielectric layer 112 is provided on the first metallization layer 109, The dielectric layer 112 does not extend beyond the first metallization layer 109 . Setting the dielectric layer 112 can raise the step of the channel region of the cell 200 , and can reduce the pressure on the channel region during chip bonding, so that the gate oxide layer 208 of the channel is not easily damaged. Dielectric layer through holes 110 are provided in the dielectric layer 112 located in the main emitter region 105 and the main gate region 102 . A second metallization layer 111 is disposed on the dielectric layer 112 , and the second metallization layer 111 is connected to the first metallization layer 109 through the dielectric layer via hole 110 . The range of t...

Embodiment 3

[0070] A specific embodiment of a photolithography plate of a power semiconductor chip. The pattern of the chip 100 described in the above embodiment 1 and embodiment 2 is divided into four equal parts with the gate bar 101 as the axis of symmetry, which are respectively the first area A0, The second area A1, the third area A2 and the fourth area A3. The patterns of the gate strip 101 and the main gate region 102 are located at the pattern splicing position, and the pattern of the photolithography plate 300 is the same as any of the equally divided patterns, as shown in the attached Figure 5 shown. The cell area does not participate in the splicing of graphics due to its small line width and complex graphics. To ensure the integrity of the pattern splicing, the edge of the photoresist plate 300 located at the adjacent pattern splicing position is also provided with an overlapping area 113 extending toward the splicing direction, as shown in the attached Figure 7 shown. as...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com